# INSTALLATION . OPERATION . MAINTENANCE

# INSTRUCTIONS

# TYPE SLB STATIC LOSS OF CONDUCTOR: BREAKER POLE FAILURE RELAY

CAUTION: It is recommended that the user of this equipment become acquainted with the information in this instruction leaflet before energizing the equipment. Failure to observe this precaution may result in damage to the equipment. Printed circuit modules should not be removed or inserted while the relay is energized unless specific instructions elsewhere in this instruction leaflet state that such action is permissible. Failure to observe this precaution can result in an undesired tripping output and cause component damage.

#### APPLICATION

The SLB pole failure relay protects against breaker pole failure, i.e. "pole disagreement". Pole failure is here defined as a pole disagreement (one or more breaker poles open while one or more poles are closed) during non fault conditions.

#### Types of Breaker Pole Disagreement

- Pole disagreement during the attempted clearing of a fault. This "breaker failure" condition is detected by conventional breaker failure relay and is cleared by tripping adjacent breakers in normal manner.

- 2) Pole failure during a breaker closure. This involves the failure of one or more poles to close during a breaker close operation, not involving a fault. This is detected by the SLB current comparison logic which trips the protected breaker after time delay, T2.

- 3) Pole failure during a breaker opening operation. This involves the failure of one or two poles to interrupt current during a breaker trip operation, not involving a fault. This is detected by the SLB current comparison logic, which calls for another attempt at tripping the protected breaker after delay T2. This attempt will probably not successfully interrupt the stuck pole (s). Therefore, the current comparison logic will continue to operate and ultimately time-out T3 which either operates 86BF to clear the adjacent breakers of alarms the operator.

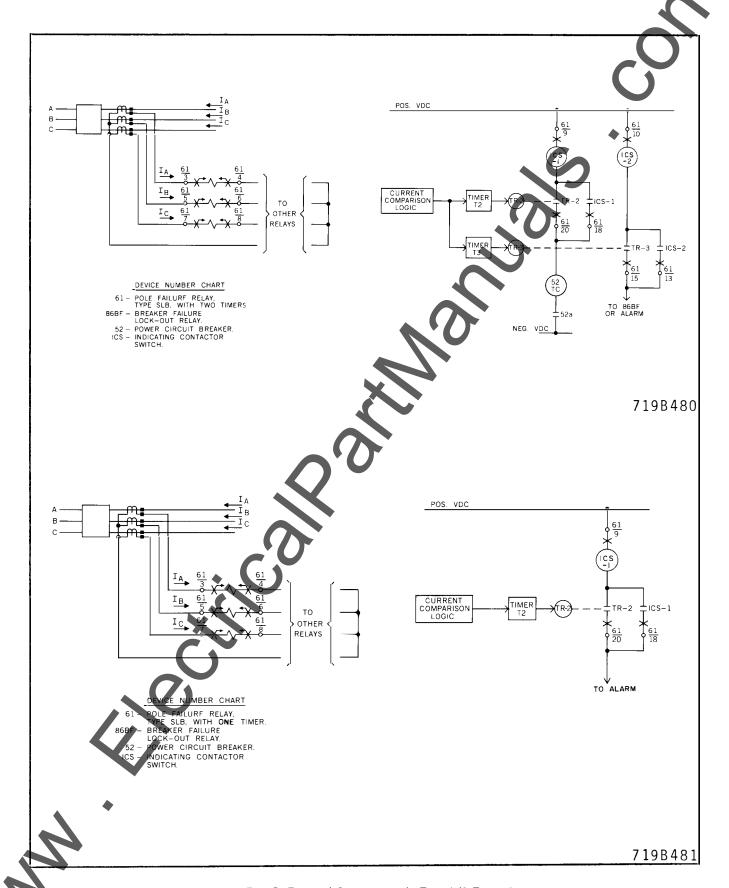

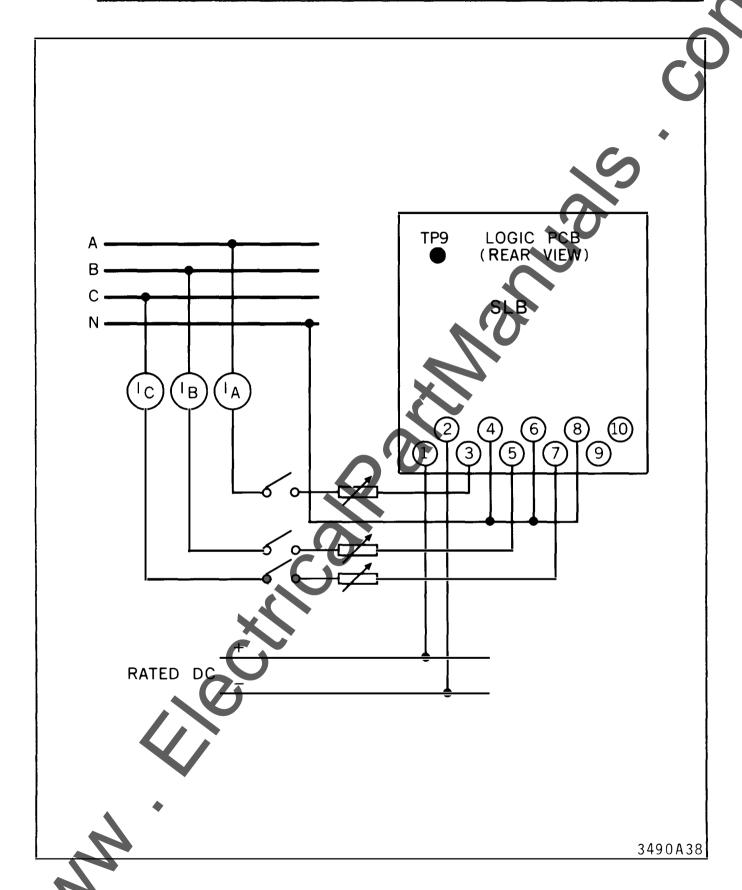

The SLB outputs are connected as shown in the external schematic diagram, figure 5.

#### Current Levels and Timing Considerations

As explained in the Operation section of this leaflet, the current comparison logic of the SLB has an output whenever one of more phase (s) carries current above the  $I_H$  level (65mA) while one or more phase (s) carries current below the  $I_L$  level (20mA). The  $I_L$  and  $I_H$  settings are factory calibrations, not intended to be changed by the customer.

The Na level  $65\,\text{mA}$ ) is determined as the lowest typical charging current expected on a transmission line. A low level is selected in order to permit the logic to detect a pole disagreement condition during time charging. The I<sub>L</sub> level (20mA) is determined by the minimum current level that the relay can reliably detect. Much lower than 20mA will cause the relay be overly sensitive and subject to pick up on extraneous signals (noise) even though the breaker is open. Of course, the I<sub>L</sub> level must not be close to I<sub>H</sub> in order to prevent incorrect current comparison outputs due to phase dissymmetries.

A current comparison output condition could occur during a ''breaker failure'' in which case it is imperative that adjacent breakers be quickly cleared in order to maintain system stability. This is achieved through conventional breaker failure protection which incorporates a timer, device 62, which is set as fast as is required to maintain stability. This is very often a low setting (12 cycles or less) and is sometimes as low as nine cycles. The pole failure timers (T2 and T3) can be set considerably higher than the breaker failure timer, since system stability is not endanagered. A suggested setting for T2 is one second.

The T3 timer, which either trips adjacent breakers via 86BF or optionally alarms to notify the operator that one of the breaker poles is stuck closed, should be set to coordinate with T2 with a comfortable margin. A suggested setting for T3 is two seconds.

#### Optional Relay Application — Alarm Only

In some instances it may be desirable to alarm-only for the pole failure condition. This is illustrated in

Fig. 5A, the external schematic for the SLB with one timer. A suggested setting for T2 is approximately one second.

#### CONSTRUCTION & OPERATION

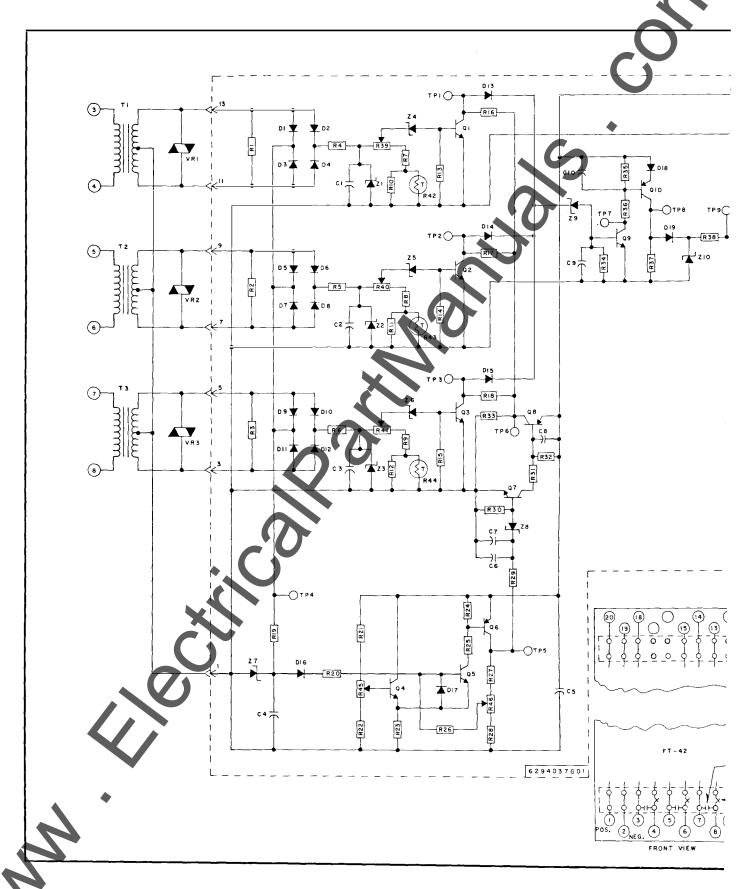

The type SLB relay is a solid state package mounted in FT42 case (See I.L. 41-076); consisting of 3 current to voltage transformers, 3 varistors, 3 sets of full wave rectifiers, 3 filters, 3 sensing circuits, 1 level detector, and a standard output circuit. It contains a 20-volt zener supply that energizes the relay logic. It also self-contains one or two timers (of same design as  $(\underline{W})$  Type TD-50 relays) for adjustable time delay applications. All 3 transformers, TA, TB, TC have a center-tapped secondary which is tied together with the DC negative for a common ground. Transformer's secondaries are connected to individual varistors to keep the secondary voltages at a safe level.

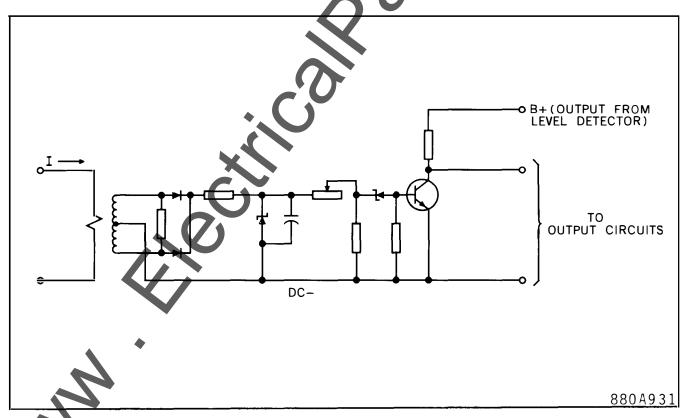

There are 2 sets of full wave rectifiers for each phase. The odd numbered diodes are used to rectify the quantities related to the  $I_H$  or high current. These quantities will be compared to a reference at the level detector. The even numbered diodes rectify quantities that will provide a signal for phase current detection. Rectified quantities are then filtered by a capacitor and the input to the current sensors is then kept at a safe value by means of zener diodes.

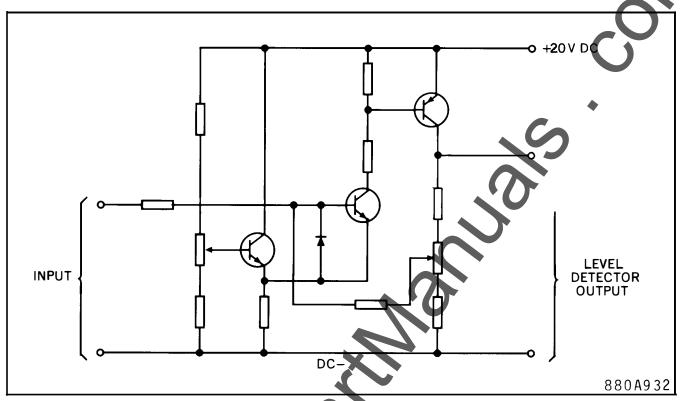

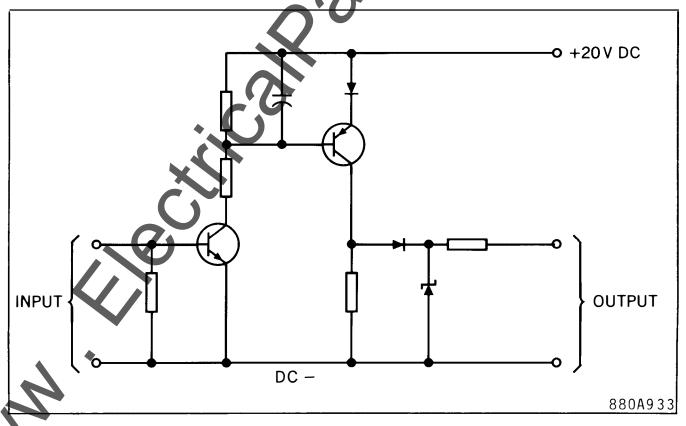

The level detector is adjusted to provide a 20 volt output whenever one or more phase current is equal or greater than 65mA. This output can then drive the relay output circuit and produce an output if at least one of the phase currents drops below 20mA as detected by the related current sensing circuit. The basic current sensing circuit consists of a transistor that is biased into a normally on condition for a phase current equal or greater than 20mA. If any phase current drops below 20mA the related transistor (Q1, Q2, or Q3) will turn off allowing any output from the level detector to deliver power to the output circuit and thus producing a relay output.

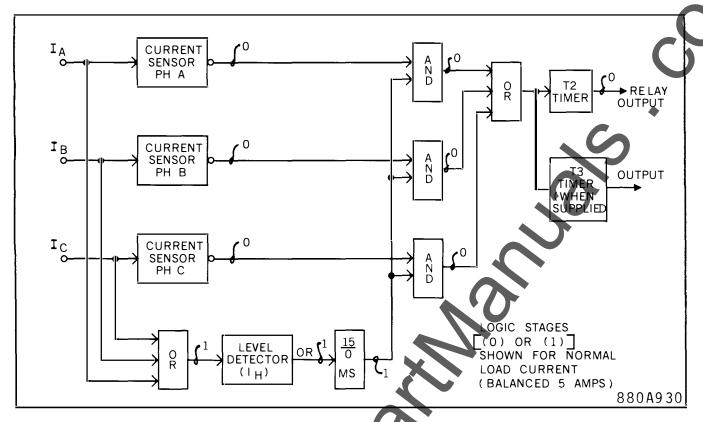

The level detector output is delayed by about 15 ms to avoid undesired tripping due to normal breaker unsymmetries. This delay circuit consists of an R-C timer, a zener diode and an output transistor. The output of this timer is used as the B+ supply for the current sensing circuits. Figures 5, 6, and 7

show some of the basic circuits described above. Relay produces telephone relay output which is delayed by means of time delay logic (self-contained timers equivalent to TD-50 relay). Standard time delay ranges are .05 to 1.0 sec. and .2 to 4 sec. For detailed characteristics of the timers refer to TD-50 relay information, (W) L-779641 and I.L. 41-579.1.

#### CHARACTERISTICS

#### A. Current Rating

Continuous 5 Amperes,  $3 \phi$ One Second 100 Amperes,  $3 \phi$

#### B. Operating Time

| Maximum              |             | 30 | MS |

|----------------------|-------------|----|----|

| Minimum<br>*Plus tin | ner setting | 15 | MS |

#### C. DC Supply

Current Burden Per Phase

| 90 MA | . 05 | VA |

|-------|------|----|

| 5. A  | 11.5 | VΑ |

#### D. DC Burden

| No timer            | 0.07 Amps. |

|---------------------|------------|

| One timer - 48 VDC  | 0.25 Amps. |

| Two timer - 48 VDC  | 0.5 Amps.  |

| One timer - 125 VDC | .195 Amps. |

| Two timer - 125 VDC | 3.80 Amns  |

#### E. Tripping Condition

At least one phase conducting 0.065 ampere or more while at least one phase is conducting less than 0.018 ampere.

#### F. Restraining Conditions

- Sudden increase of current from 0.0 ampere to any value greater than 0.065 ampere in all phases, whether balanced or not.

- Any sudden change in current, increase or decrease, balanced or not, as long as the minimum current is greater than 0.065 ampere in all three phases.

- 3) Simultaneous interruption of all three currents, balanced or not.

#### G. Settings

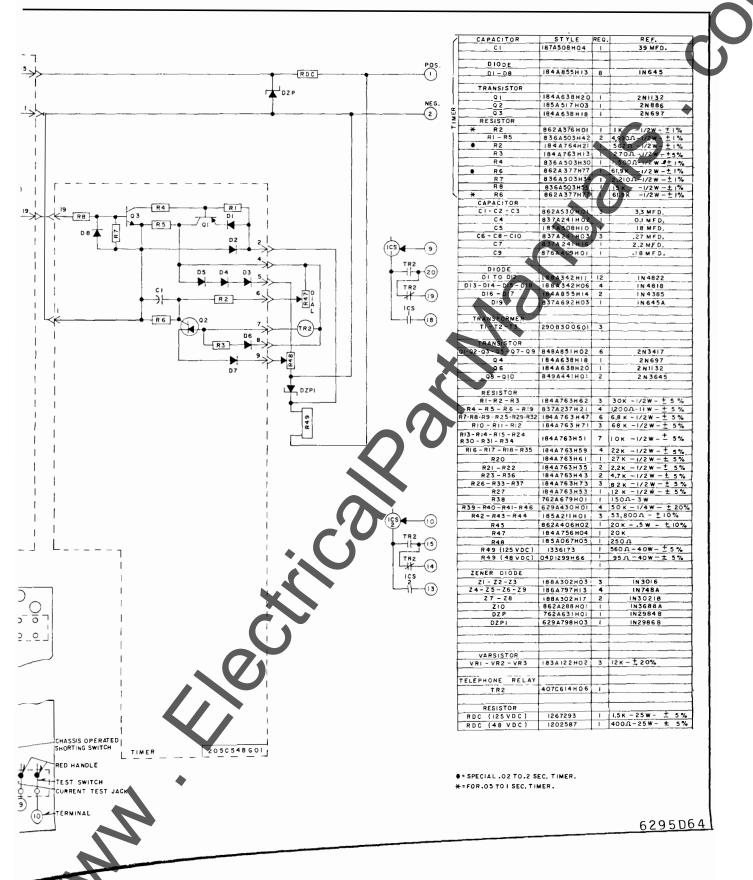

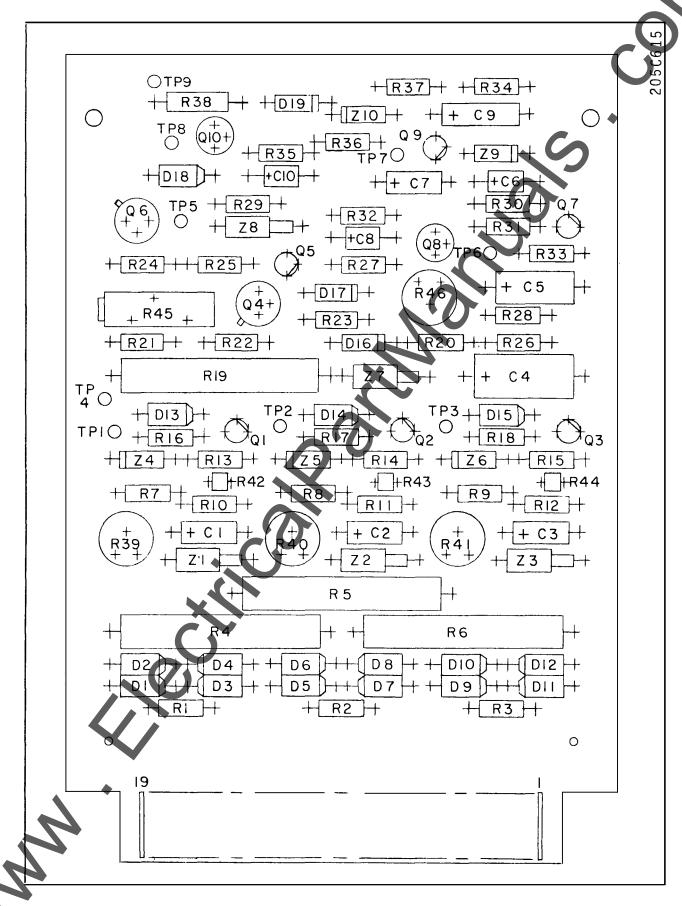

Proper time delay is selected by turning the knob of potentiometers R47 and R50 (dialed).

TYPE SLB

#### **External Connections**

Fig. 4 shows the external connections for the type SLB relay.

#### Receiving Acceptance

Make a visual inspection to make sure that there are no loose connections, broken resistors, or broken resistor wires.

Check relay per following procedure:

- A. Refer to figure 10 in this I.L.

- B. Connect per test figure and apply rated DC voltage.

- C. Apply IA = 15mA, IB =  $I_C$  = 100mA. A 20 volt output should be observed at logic PCB terminal #19, and telephone relay TR2 (and TR3 for 2 timer relays) should operate.

- D. Apply  $I_B = 15\text{mA}$ ,  $I_A = I_C = 100\text{mA}$ , and check relay output per step C.

- E. Apply  $I_C = 15\text{mA}$ ,  $I_A = I_B = 100\text{mA}$ , and check relay output per part C.

#### INSTALLATION

The relays should be mounted on switchboard panels or their equivalent in a location free from moisture. Mount the relay by means of the four mounting holes on the flange for semi-flush mounting or by means of the rear mounting stud or studs for projection mounting. Either a mounting stud or the mounting screws may be utilized for grounding the relay. The electrical connections may be made directly to the terminals by means of screws for steel-panel mounting or to the terminal studs furnished with the relay for thick panel mounting. The terminal studs may be easily removed or inserted by locking two nuts on the stud and then tunning the proper nut with a wrench. For detailed FT case information, refer to I L. 41-076.

#### Routine Maintenance

All relays should be checked at least once every year or at such time intervals as may be dictated by experience to be suitable to the particular application.

### Calibration - Refer to Fig. 10

Use the following procedure for calibrating the relay if the relay adjustments have been adjusted or disturbed. This procedure should not be used unless it is apparent the relay is not in proper working order.

#### Level Detector\_

1. Energize relay with rated DC voltage.

- 2. Apply  $I_A = 65\text{mA}$ ,  $I_B = I_C = 0$

- 3. Monitor relay output (PCB TP19 top left) and adjust R45 (trim-pot same board) until relay output (full output) is just observed.

- 4. Reduce IA to about 63mA and adjust R46 (same board top right), until output drops to zero.

- 5. Increase IA and relay output should be observed as current reaches 65mA.

- 6. Reduce IA and recheck per step 4.

- 7. In general adjust R45 for pickup, and R46 for drop out until relay produces an output (full output) as current approaches 65mA and drops out quickly if current is, then, reduced.

#### B. Current Sensors (fig. 10)

- Apply rated DC voltage.

- 2. Apply  $I_A = 20mA$ ,  $I_B = I_C = 1$  Amp. Monitor relay output (TP9, by PCB).

- 3 Adjust R39 (circuit board bottom left) until the first output indication (or first meter deflection), is <u>just</u> observed. If relay was already picked up, adjust R39 until it drops out, and then adjust it again as specified above.

- 4. Reduce current IA, observing the relay output. Complete relay output (Vo = 20) should be observed within 3mA. Recheck first output indication at 20mA.

- 5. Adjust R40 (bottom center) per steps 3 and 4, this time setting  $I_A = I_C = 1$  Amp,  $I_B = 20 \text{mA}$ .

NOTE: Output telephone relays should also operate everytime full trip was indicated by TP9 (PCB-logic), for duration of timer setting(s).

#### Renewal Parts

Repair work can be done most satisfactorily at the factory. However, interchangeable parts can be furnished to customers who are equipped for doing repair work. When ordering parts, always give the complete nameplate data.

#### References

FT case I.L. 41-076

TD-5 Timer I.L. 41-579.1

TD-50 Timer L-779641

#### **PARTS LIST**

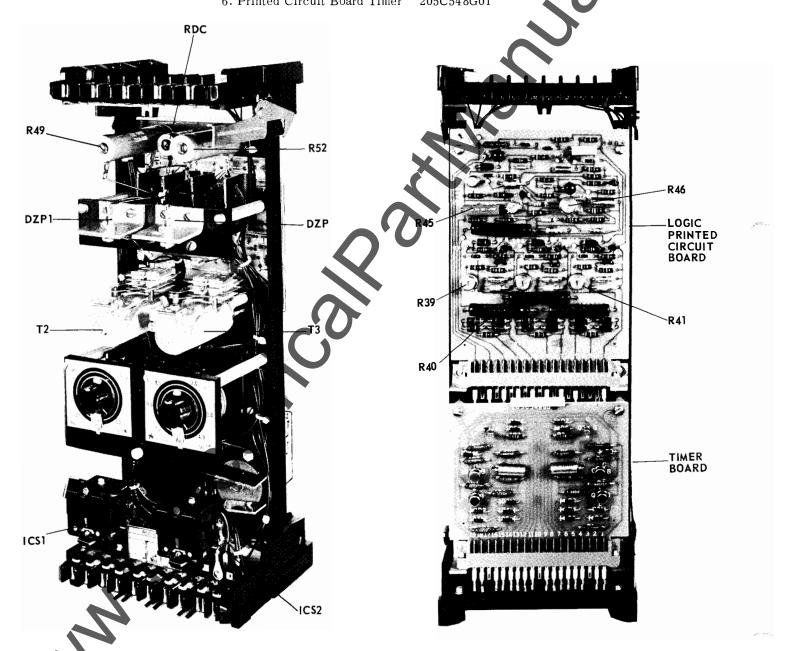

Fig. 1 Relay Picture

## Part Name (<u>W</u>) Style or Reference

1. Transformer (TA,TB,TC) 290B300G01 2. Varistor (VR1, VR2, VR3) 183A122H01 3. Zener (20V, 10W) 762A631H01 4: DC Resistor 48V 1202587 125V 1267293 250V 1202954

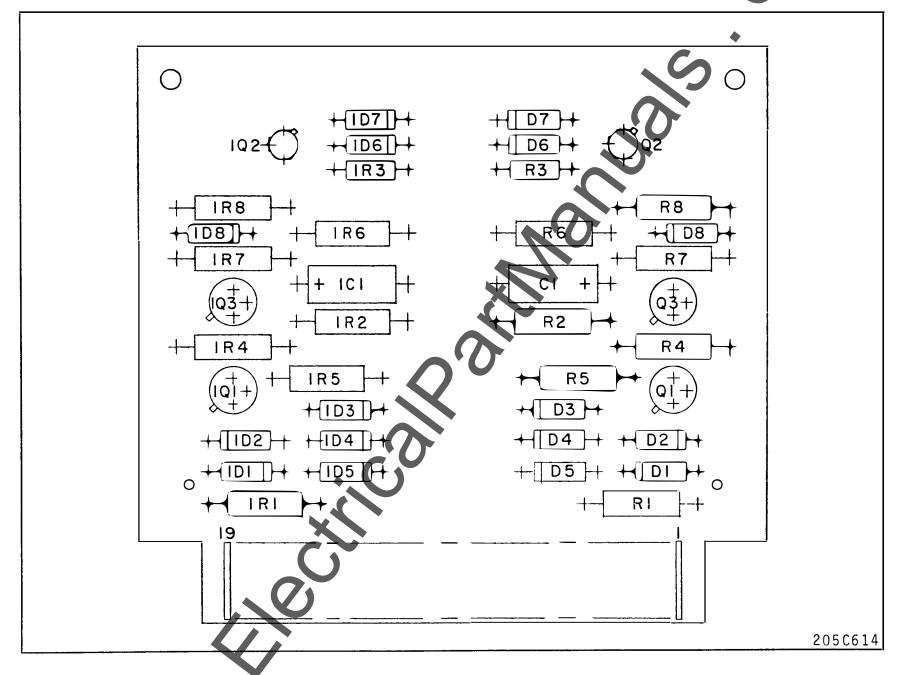

5. Printed Circuit Board Logic 6294D37G016. Printed Circuit Board Timer 205C548G01

Fig. 2 Relay Picture

Fig. 3 Internal Sch

Fig. 5 External Connections (1 Timer) (2 Timers)

Fig. 6 Logic Block Diagram

Fig. 7 Basic Current Sensor Circuit

Fig. 8 Level Detector

Fig. 9 Standard Output Circuit

Fig. 10 Component Location Timers

Fig. 12 Relay Test Figure

RELAY-INSTRUMENT DIVISION

RELAY-INSTRUMENT DIVISION

NEWARK, N. J.