#### INSTALLATION . **OPERATION**

# INSTRUCTIO

## TYPE SDBU-2 STATIC BLINDER RELAY

CAUTION: It is recommended that the user of this equipment become acquainted with the information in this instruction leaflet before energizing the equipment. Failure to observe this precaution may result in damage to the equipment.

### APPLICATION

The SDBU-2 relay provides the following functions in conjunction with the logic provided by the SRU relay:

- 1. Restricted trip function

- 2. Out-of-step blocking of tripping

- 3. Out-of-step blocking of reclosing

- 4. Out-of-step tripping

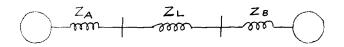

The SDBU-2 characteristic consists of two sets of two essentially parallel lines (actual arcs of extremely large circles) which form an angle with respect to the R-Axis on an R-X plot which is adjustable from 60° to 90°. The factory adjustment is 75°. Each set of parallel lines is equally spaced on each side of the origin of the R-X diagram. The relay has one output transistor per each set of the outside and inside set of parallel lines. Each output ties the output terminal to the negative through the conducting NPN transistor when relay is in the non-operate condition. Relay provides two outputs of 15.0 to 190 volts dc and up to 0.01 ampere of current when subjected to an ohmic value that falls inside each set of two characteristic lines.

The settings of the SDBU-2 relay define the ohmic reach from the origin in a direction perpendicular to the transmission line characteristics

## CONSTRUCTION

The SDBU-2 relay consists of five air gap transformers (compensators), four center tapped auto-transformers, five phase shifting circuits, five isolating transformers, and several printed circuit assemblies.

Printed circuit boards are plug-in types which may be removed for tests or examination and then reinserted. They may also be plugged into a card extender, style #849A534G01, to make the test points and components accessible for in-service checking.

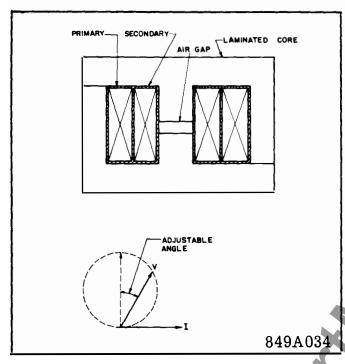

### Compensator

The compensators which are designated IPOL,  $+T_{AB1}$ ,  $-T_{AB1}$ ,  $+T_{AB2}$  and  $-T_{AB2}$ are two winding air-gap transformers (Fig. 5). There are two primary current windings, each having seven taps which terminate at the tap block. They are marked 1.51, 2.00, 2.50, 3.50, 5.00, 7.1, and 10.0. IPOL compensator has no taps. A voltage is induced in the secondary which is proportional to the primary tap and current magnitude. This proportionality is established by the cross-sectional area of the laminated steel core, the length of the air gap which is located in the center of the coil, the tightness of the lamination. All of these elements have been precisely set at the factory. The clamps which hold the laminations should not be disturbed by either tightening or loosening the clamp screws.

The secondary winding of the IPOL compensator is center-tapped to provide a voltage supply for the phase shifting network. The phase shifting network produces voltage in phase with the primary compensator current.

NEW INFORMATION **EFFECTIVE: AUGUST 1968**

### Phase Shifting Circuits

Phase shifting of the input voltages is obtained through a circuit that consists of center-tapped autotransformers  $X_{A2}$ ,  $X_{A3}$ ,  $X_{A4}$ ,  $X_{A5}$ , resistors P2 and capacitor  $C_{2A}$ , and resistor P3 and capa  $C_{3A}$ , resistor P4 and capacitor  $C_{4A}$ , resistor P5 and capacitor  $C_{5A}$  respectively.

In the current polarizing circuit the compensator voltage output is phase shifted by means of resistor  $R_{1\,A}$  and capacitor  $C_{A\,1}.$  The compensator voltage is supplied through the center tapped secondary of  $I_{\, \hbox{POL}}$  compensator.

### Isolating Transformers

Transformers T1, T2, T3, T4, and T5 serve two purposes. First, they isolate the ac circuits from the dc circuit. Second, they amplify the clipped ac signal to make the relay sensitive to low level input signals.

### Printed Circuit Board Assembly

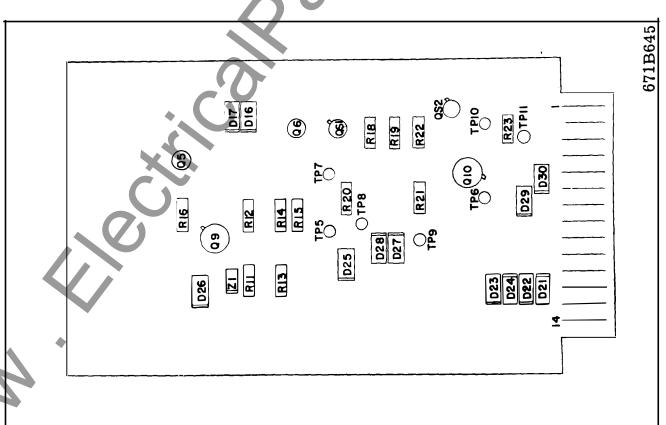

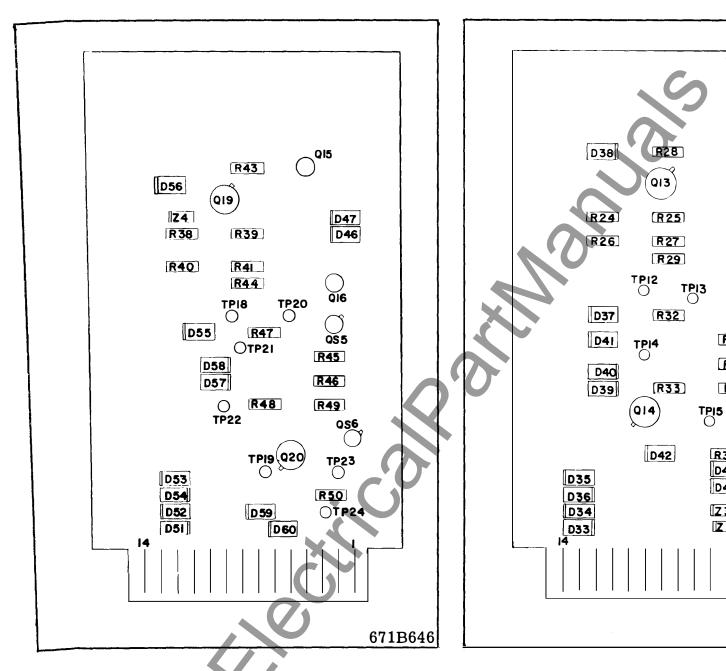

The SDBU-2 relay uses six printed circuit boards (PCB) assemblies. The six PCB's are: one operating board, four polarizing boards; one is marked "+1" and one is marked "-1". These two boards refer to two inside characteristic lines of the relay. Further, one board is marked "+2" and one is marked "2". These two boards refer to two outside characteristic lines of the relay.

One "output board" contains two outputs. Output #1 (relay terminal #5) represents the inside characteristic and output #2 (relay terminal #6) represents the outside characteristic of the relay.

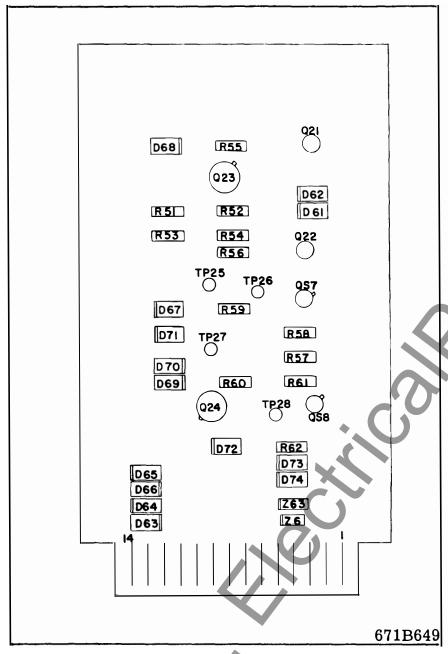

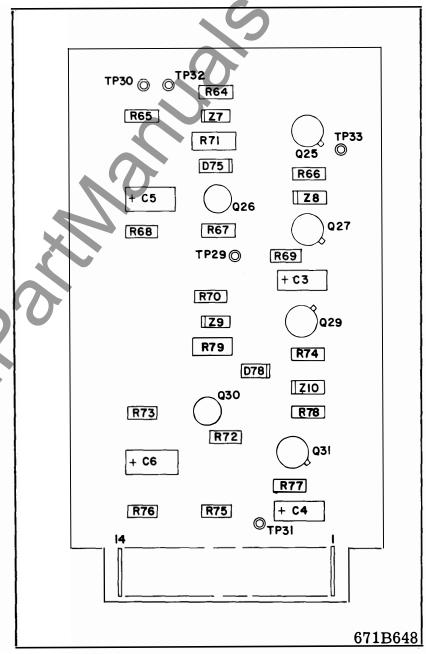

PCB assemblies shown in Figures 10 to 15 contain all the resistors, diodes, transistors, and thyristors necessary to perform the intended functions.

Components on each board are identified by a letter followed by a number so that every component has an exclusive identification. Resistors are identified by the letter R followed by a number. Similarly, diodes are identified by a D, and the cathode (the end out of which conventional current flows) is identified by a bar across the point of an arrow. Zener diodes are identified by Z, transistors by Q, thyristors by Qs, capacitors by C, and test points by TP.

Component letter designations are listed as below

Capacitor C

Diode D Thyristor QS

Resistor R Transistor Q

Test Point TP Zener Diode Z (or DZ)

### **OPERATION**

Four identical logic systems are used in the SDBU-2 relay. Each of the systems modifies the distance relay reach along the lines (T &U) as shown on Fig. 6. Two systems restrict the distance relays operation to the area left of T1 and T2 and two systems to area right of U1 & U2. Each of the systems presents a voltage to the static phase angle comparison unit which checks their phase angle relation to the operating voltage produced by  $I_{\text{PO}}$ . Each system voltage is composed of the phase shifted phase-to-phase voltage and the compensator output voltage that is proportional to the R component of the transmission line characteristic.

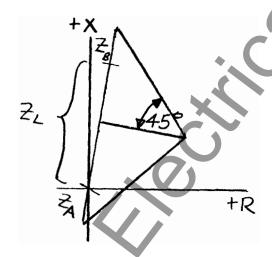

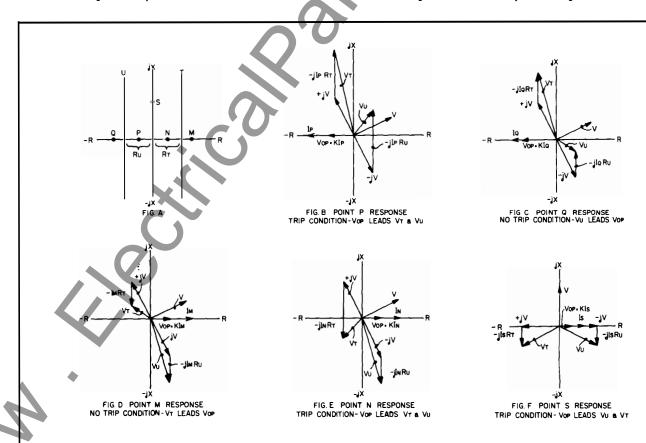

Complete operation of the relay is best illustrated by the set of phasor relations for selected conditions, as shown on Fig. 7. For simplicity assume relay characteristic is 90°, and operation of one unit only is considered.

Fig. 8 shows R-X diagram and several selected points Q, P, N, M, S located within the outside the operating area of the SDBU-2 relay designated by lines U and T. Depending on fault location currents are designated as  $I_D$ ,  $I_G$ ,  $I_m$ ,  $I_n$ , or  $I_S$ .

Relay tripping conditions occur when the phasor designated VOP leads phasor VU and VT simultaneously. Phasor  $V_{OP} = KI_D$  is derived from the compensator designated "IPOL" and phase shifted by means of phase shifting circuit P1 and C1 to be in phase with the primary current I. Phasor V II controls the relay characteristic along the line designated as U. V<sub>T</sub>phasor controls the relay characteristic along the line designated as "T". "V It" phasor consists of reversed relay terminal voltage (V) phase shifted by  $90^{\circ}$  and modified by compensator output-jI R . R represents the reach of the compensator designated as "-TAB" that is set for the desired value " $R_U$ " along the R-axis. " $V_T$ " vector consists of relay terminal voltage ("V\*) phase shifted by  $90^{\circ}$  and modified by compensator output -jI<sub>n</sub>R<sub>T</sub>.

R represents the reach of the compensator designated as "+ $T_{AB}$ " that is set for the desired value " $R_{T}$ ", along the R-axis.

For a fault at point "P" (Fig. (B) within the relay trip characteristic) the "- $T_{AB}$ " compensator voltage  $I_pR_U$  is added to -jV phasor so that the sum of these two phasors results in a phasor  $V_U$  that lags the  $V_{OP}$  phasor fulfilling the tripping conditions. Since phasor  $V_T$  was already in the lagging condition and the compensator voltage from + $T_{AB}$  compensator  $I_pR_T$  has only increased its magnitude without changing its relative position with respect to  $V_{OP}$ .

Fig. (C) shows relay response to a fault at point "Q" (located beyond the relay characteristic) since there is not enough current to produce reversal of the  $V_U$  phasor there will be no tripping output because  $V_U$  phasor leads phasor  $V_{OP}$ .

Fig. (D) shows similar relay response (no trip) for point "M" (located beyond the relay characteristic) since there is not enough compensation to cause phasor  $V_T$  to lag phasor  $V_{OP}$ .

Fig. (E) shows the relay response to a fault at point "N". In this case relay response is similar to the point "P" response. The compensator output voltage  $I_nR_T$  is large enough to produce a phasor  $V_T$  that lags phasor " $V_{OP}$ ".

Fig. (F) point "S" illustrates response of a 90° lag fault. When there is no fault current, the relay is inoperative since  $V_{OP} = O$ . In the presence of a small amount of current,  $V_{OP}$  appears and a small compensation makes  $V_T$  and  $V_U$  lag  $V_{OP}$  and produce a tripping condition.

### Phase Angle Comparison Unit

Referring to Fig. 4 the phase angle comparison unit is tripped when current flows into the base of transistor Q27 through zener diode Z3. Such tripping current must come from the 20V bus through either transistor Q2 or Q4 located in the "operate" circuit. The operate circuit, driven by transformer T1, is continually trying to trip the unit by supply current through Q2 on alternate half cycles. Q2 on alternate half cycles. Q2 conducts when the polarity marked terminals of T1 are positive.

When Q2 conducts, a portion of the current goes through resistor R20. This current,  $I_{R20}$ , may take

either of two paths to the negative bus. If QS1 is in a conducting state,  $I_{R20}$  passes through it directly to the negative bus. If QS1 is in a blocking state,  $I_{R20}$  passes through D43 and then through Z3 to transistor Q27 to cause tripping. Thyristor QS1 is located in the "polarizing circuit +1" of the relay. This circuit is driven by transformer T2.

To prevent the operate circuit from causing tripping, the polarity marked terminals of T2 must go positive before the polarity terminals of T1 do. This causes Q5 to conduct current through R16 and drive the base of Q9. Q9 then conducts current from the 13V bus through R19 to gate QS1 into conduction. When QS1 conducts, it short circuits the current which might otherwise pass through D43 to cause tripping. Once QS1 begins to conduct, the gate loses control and it remains in the conducting state until the current is turned off by Q2. No tripping output can develop as long as the T2 voltage leads the T1 voltage.

The operate circuit switches for the next half cycle so that transistors Q3 and Q4 conduct in an attempt to cause tripping. In the polarizing circuit, Q6, Q10, and QS2 seek to prevent tripping by short circuiting the current which might otherwise pass through D44, Z3, and Q27.

Polarizing unit marked "-1" provides similar action as unit "+1".

Notice that QS3 and QS4 units provide similar action as QS1 and QS2. Since QS1 and QS3, and QS2 and QS4 units are connected in parallel, so that two tripping outputs per half cycle are needed to make operation of Q27 possible.

Polarizing boards marked "+2" and "-2" act in similar manner as the boards "+1" and "-1", except they control Q31 transistor that provides output for unit #2 (the outside characteristic lines).

### Restraint Squelch

When the operate circuit transistor Q2 conducts, approximately 18V is applied through diode D25 to back bias D26 and prevents Q9 from turning on. Thus a trip signal, initiated because the T1 voltage is leading, cannot be improperly interrupted when the T2 voltage goes positive. A full half cycle tripping output is therefore produced by Q . This back biasing connection is called the restraint squelch

circuit. The same is true for D30, D29, and Q4 & Q10 on the alternate half cycle.

Similar function is performed by D55, D56, Q19 and D59, D60, Q20 board "+2" and D67, D68, and Q23, and D72, D71, Q24 on board "-2".

The operate circuit and the polarizing circuit are both duals having identical circuits which operate on alternate half cycles. The restraint squelch works into each of the duals in the same way.

Transformer T3 receives a polarizing signal from the circuit which is identical to the one that supplies transformer T2. The phase angle relation between the T1 voltage and the T3 voltage is compared in the same manner as described above and tripping signals are supplied through D44 and D43, through DZ3 and to Q27. This polarizing circuit contains a restraint squelch identical to one described for the T2 circuit.

### D.C. Voltage Detector

Transistor Q25 and zener diode Z7 for output #1, and Q29 and zener diode Z9 for output #2 monitor D.C. voltage level. If the d-c voltage drops too low for the logic to operate properly, it will cause Q25 or Q29 in turn off and thereby send a gate signal to the restraint thyristors through D27, D28 for output #1 and D58 and D57 for output #2.

### Output Circuit

Output for unit #1 is provided by Q26 (Relay terminal #5) and for unit #2 by Q30 (Relay terminal #6.) The output transistor provide 15 to 19 V. d.c. and up 0.010 amperes d.c.

The operation of Q26 and Q30 transistor is effected when tripping signals provided by relay logic operate transistor Q27 for output #1, and Q31 for output #2.

### **CHARACTERISTICS**

The relay is energized by phase-to-phase voltage and delta current. It measures the same impedance for phase-to-phase or three phase faults.

Tap plate settings are related to the characteristics of the relay as shown in Fig. 6 as follows:

T2 and U2 represent characteristic of unit #2, and T1 and U1, represent characteristic of unit #1.

+TA1, +TA2, +TB1, and +TB2 values represent compensator tap settings.

Relay tap setting "T" relates to "R" component on the R-X diagram for different maximum sensitivity angle compensation as follows:

for

$$90^{\circ}$$

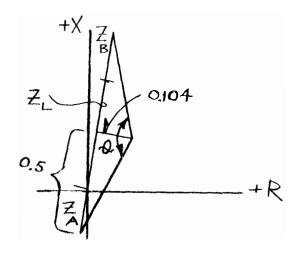

- angle  $R = 1.0T$   $75^{\circ}$  - angle  $R = 1.04T$   $60^{\circ}$  - angle  $R = 1.12T$

Relay is shipped with maximum sensitivity angle of  $75^\circ$  and can be readjusted continuously between  $60^\circ$  and  $90^\circ$ , as outlined in calibration procedure.

All tap plate settings can be set independently.

Tap plate markings are as follows:

### Sensitivity

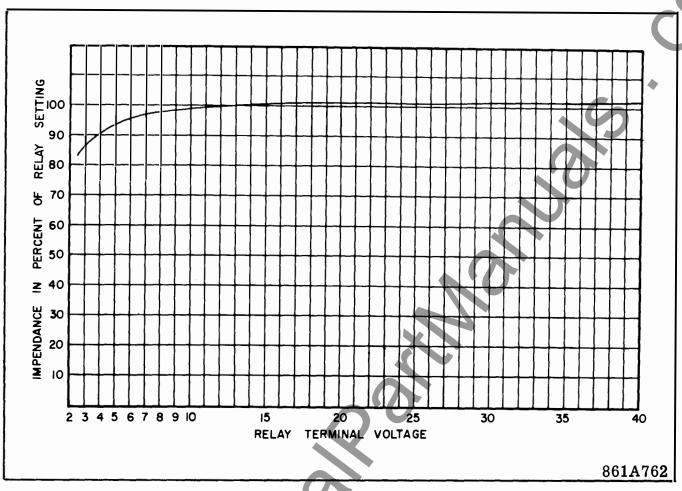

A plot of relay reach in per cent of tap block setting vs. relay terminal voltage at 0 degrees is shown on Fig. 8.

### Time of Operation

The operating time of the relay varies from 2 msec. to 9 mseconds for faults near the balance point.

# CURRENT CIRCUIT RATING IN AMPERES

| TAP SETTING | CONTINUOUS | 1 SECOND |

|-------------|------------|----------|

| 10.0        | 5          | 240      |

| 7.1         | 6          | 240      |

| 5.0         | 8          | 240      |

| 1.51 - 3.50 | 10         | 240      |

### Burden Data

### Current Burden (Per Phase)

Measured at 5 amp/ $\underline{0}$  and Voltage 120  $\underline{/0}$  applied to relay.

# TAP SETTING IMPEDANCE RESISTANCE REACTANCE

| T    | ${f z}$   | R         | X         |

|------|-----------|-----------|-----------|

| 10.0 | .364 ohms | .252 ohms | .262 ohms |

| 7.1  | .224      | .172      | .144      |

| 5.0  | .158      | .133      | .086      |

| 3.5  | .116      | .103      | .053      |

| 2.5  | .094      | .086      | .038      |

| 2.0  | .084      | .077      | .033      |

| 1.5  | .076      | .071      | .028      |

### Potential Circuit Burden

At  $120/\underline{0^{\circ}}$  volts and current circuits energized with  $5/\underline{0^{\circ}}$  amps. the potential burden is 30 voltamperes, 16.8 watts and 24.9 vars.

### D.C. Current Burden

D.C. current burden is 0.07 amperes at all rated d.c. voltages.

# SETTING THE RELAY AND CALCULATIONS

Relay reach is set on the tap plate. The tap plate markings are:

$$+T_{A1} + T_{B1} + T_{A2} + T_{B2}$$

$-T_{A1} - T_{B1} - T_{A2} - T_{B2}$

Maximum sensitivity angle is set for  $75^{\circ}$  (current lagging voltage) in the factory. This adjustment need not be disturbed for line angle  $65^{\circ}$  or higher. For line angles below  $65^{\circ}$  recalibrate for  $60^{\circ}$  - maximum sensitivity angle.

The tap plate settings (T) represent the reach perpendicular to maximum sensitivity angle and can be converted to the reach along the R-axis as follows:

for

$$90^{\circ}$$

- calibration  $R = 1.0T$

$$75^{\circ}$$

calibration  $R = 1.04T$

$$60^{\circ}$$

- calibration  $R = 1.12T$

Settings of +TA1, TB1 - TA1 and - TB1 control the inside (#1) characteristic of the relay.

$$+T_{A1}$$

and  $+T_{B1}$  control the reach along "+R" axis.

$-T_{A1}$  and  $-T_{B1}$  control the reach along "-R" axis.

+TA2, +TB2, - TA2, and - TB2 controls the outside (#2) characteristics of relay.

"+TA2 and +TB2 control the reach along "+R axis.

-TA2 and -TB2 control the reach along "-R" axis.

Letter "A" refers to phase "A" setting and letter "B" to phase B setting. All "+T" settings can be made independently from "-T" settings if required.

### Compensator Setting

Each set of compensator taps terminates in in inserts which are grouped on a socket and form approximately three quarters a circle around a center insert which is the common connection for all of the taps. Electrical connections between common insert and tap inserts are made with a link that is held in place with two connector screws, one in the common and one in the tap. There are two TB settings to be made since phase B current is passed through two compensators. A compensator tap setting is made by loosening the connector screw in the center. Remove the connector screw in the tap end of the link, swing the link around until it is in position over the insert for the desired tap setting, replace the connector screw to bind the link to this insert, and retighten the connector screw in the center. Since the link and connector screws carry operating current, be sure that the screws are turned to bind snugly.

### Setting Example

## CRITERION FOR SETTING BLINDERS FOR OUT-OF-STEP RELAYING

- Inner blinder must be set to accommodate maximum fault resistance for internal 3-phase fault.

- 2. Inner blinder should not operate on most severe stable swing.

- Outer blinder must have adequate separation from inner blinder for fastest out-of-step swing to be acknowledged as an out-of-step condition.

- 4. Outer blinder must not operate on load.

A reasonable approximation of arc resistance at fault inception is 400 volts per ft. If a maximum ratio (line voltage/ (spacing) is 10,000 volts per ft. for a high voltage transmission line and if a min. internal 3-phase fault current is calculated as:

$$I_{min} = \frac{E}{(Z_A + Z_L)} \sqrt{3} \quad \mbox{where } Z_A \mbox{ is maximum source impedance } Z_L \mbox{ is line impedance, and } E \mbox{ is line-to-line voltage.}$$

Then:

$$R_{max} = \frac{400 \text{ x Ft.}}{I_{min}} = \frac{400 \text{ x Ft.}}{E} \sqrt{3} (Z_A + Z_L)$$

$$R_{\text{max}} = \frac{693}{10,000} (Z_A + Z_L) = .0693 (Z_A + Z_L)(1)$$

Adding a 50% margin to cover the inaccuracies of this expression.

$$R_{max} = 0.104 (ZA + Z_{I})$$

Secondary ohms =

$$R_{max} \frac{R_C}{R_v} = R_S$$

where RC - C.T. Ratio

If the relay has maximum sensitivity angle setting of  $75^\circ$  then relay tap setting T=RS

Use next T-compensator setting (+TA1, +TB1 and - TA1 - TB1). This setting controls #1 unit reach.

This is the minimum permissible inner blinder setting where it is used to provide a restricted trip area for distance relay.

Another criterion that may be considered is based upon the rule of thumb that stable swing will not involve an angular separation between generator voltages in excess of 120 degrees. This would give an approximate maximum of:

Zinner =

$$\frac{Z_A + Z_L + Z_B}{2\sqrt{3}} = .288 (Z_A + Z_L + Z_B)(2)$$

where  $Z_B$  is the equivalent maximum source impedance at the end of the line away from  $Z_A$ .

In terms of secondary ohms

$$Z_{inner}$$

(secondary) =  $\frac{R_C}{R_V}$   $Z_{inner}$

In this case Z (secondary) - directly corresponds to the T - tap plate setting without conversion to R-setting. Use the nearest T-setting.

In this case again T-setting to be used are for #1 unit (+TA1 + TB1 - TB1 - TB1).

An inner blinder setting between the extremes of (1) and (2) may be used. This provides operation for any 3-phase fault which arc resistance, and restraint for any stable swing. To accommodate the faster out-of-step swings while retaining an acceptable outer blinder setting the lower setting is recommended.

For slow out-of-step swings a reasonably close placement of this outer to the inner blinder characteristic is possible. The separation must however be based on the **fastest** out-of-step swing expected. A 50 millisecond interval is inherent in the out-of-step sensing logic and the outer blinder must operate 50 ms or more ahead of the inner blinder.

Since the rate of change of the ohmic value manifested to the blinder elements is dependent upon accelerating power and system WR it is impossible to generalize. However, based on an inertia constant (H) equal to 3 and the severe assumption of full load rejection, a machine will experience, assuming a uniform acceleration, an angular change in position of no more than 20 degrees per cycle on the first half slip cycle.

If the inner blinder were set for 0.104 ( $Z_A + Z_L + Z_B$ ) and the very severe 20 degrees per cycle were used, the simple trigonemetric manipulation of Appendix I reveals that the outer blinder should be set for approximately:

$$Z_{outer} = 0.5 (Z_A + Z_L + Z_B)$$

Note that the 0.104 ( $Z_A + Z_L + Z_B$ ) expression includes  $Z_B$  which was not present in the minimum relationship. **Using** the actual minimum for the inner blinder setting provides further margin.

It will usually be possible to use the minimum blinder setting of 1.5 ohms (secondary). Based on the 20 ohm per cycle criterion and the logic requirement of 50 milliseconds, Appendix II shows that the minimum outer blinder setting is:

$$\begin{split} Z_{outer} &= 0.55 Z_T \, \frac{3 Z_T \, + \, 9}{3 Z_T \, - \, 3} \, \sqrt{3} \\ &\quad \text{where } Z_T \text{ is } (Z_A + Z_L + Z_B) \end{split}$$

It should be recognized that with the OS-2 logic, no commitment to trip on out-of-step occurs until the inner blinder operates. Therefore, a stable swing for which the outer blinder operates imposes no problem.

Also it should be emphasized that where a distance relay is used to supervise the out-of-step relaying, the distance relay 3-phase element and the outer blinder must operate 50 milliseconds or more prior to the inner blinder. This may require a somewhat longer reach on the distance relay than would otherwise be required.

Here again, the  $Z_{\text{Outer}}$  settings should be converted to secondary ohms.

$$Z_{outer}$$

(secondary) =  $Z_{outer} \frac{R_C}{R_V}$

In this case Z (secondary) - outer directly corresponds to T-tap plate setting without conversion to R-setting. Use the next highest T-setting but make sure it is higher than the  $Z_{inner}$  blinder setting.

Set  $+T_{A2}$ ,  $+T_{B2}$ ,  $-T_{A2}$ ,  $-T_{B2}$  (unit #2 settings) for outside blinder settings.

### Line Angle Adjustment

Maximum sensitivity angle is set for  $75^{\circ}$  (current lagging voltage) in the factory. This adjustment need not be disturbed for line angles of  $65^{\circ}$  or higher. For line angles below  $65^{\circ}$  set for a  $60^{\circ}$  maximum sensitivity angle by adjusting the pteentiometer P1. Refer to calibration procedure when a change in maximum sensitivity angle is desired.

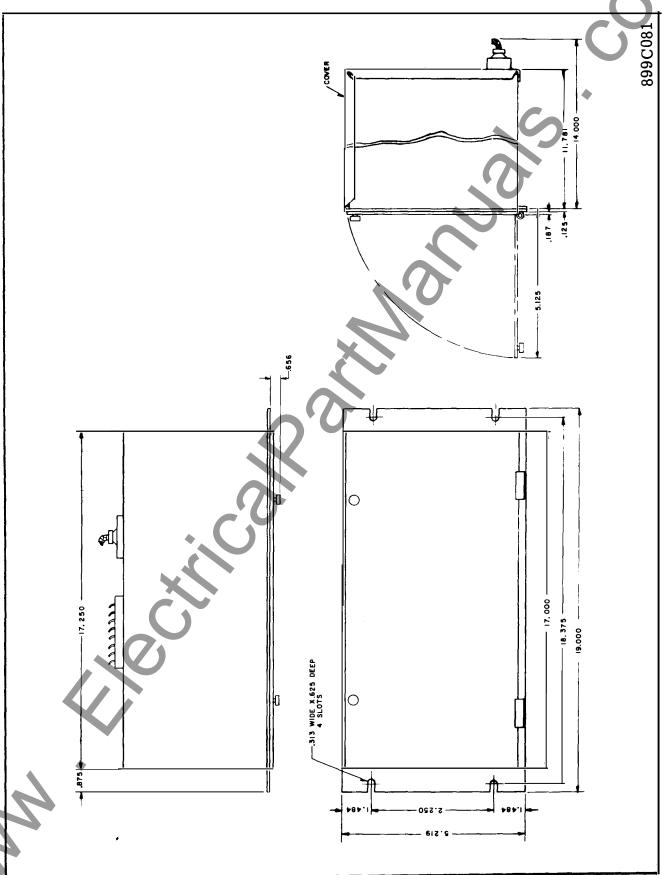

### INSTALLATION

The relays should be mounted on switchboard panels or their equivalent in a location free from dirt, moisture, excessive vibration and heat. Mount the relay by menas of the four slotted holes on the front of the case. Additional support should be provided toward the rear of the relay in addition to

the front panel mounting. This will protect against warping of the front panel due to the extended weight within the relay case.

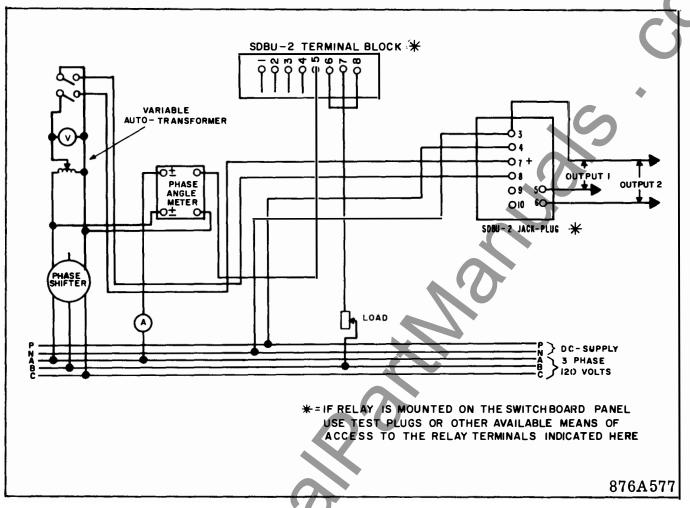

## EXTERNAL CONNECTIONS

Figure 9 shows the external connections for an SDBU-2 relay.

Current circuit connections are made to an eight section terminal block located at the rear. Potential circuits, both a-c and d-c as well as input and output logic signal circuits, are connected through a 24-terminal jack. Connections are made by a plug on the wiring harness. The plug is inserted between the two latching fingers which hook over the back of the plug to prevent an accidental loosening of the plug. The plug can be removed by spreading the two fingers apart enough to disengage the hooks from the back. The plug must be withdrawn while the fingers are spread apart.

Note that terminal number 1 is connected to the case within the relay and may be used for grounding the shields of connecting cables. The grounding connection will be broken when the plug is disconnected.

Permanent grounding of the case is accomplished by connecting a ground wire under a washer of a cover screw. These are self-tapping screws and provide excellent low resistance contact with the case.

### RECEIVING ACCEPTANCE

- 1. Give visual check to the relay to make sure there are no loose connections, broken resistors, or broken wires.

- Perform electrical acceptance test that consists of an electrical test to make certain that the relay measures the balance point impedance accurately, and hi-pot tests.

### Recommended Instruments for Testing

Westinghouse Type PG-161 - S#291B749A33 or equivalent a.c. voltmeter.

Westinghouse Type PA-161 - S#291B719A21 or equivalent a.c. ammeter.

### Hi-Pot Tests

**CAUTION:** Before making Hi-Pot tests, connect together jack terminals 3, 4, 5, 6 to avoid destroying components in the static network. These connections are not necessary for surge testing. Besides, connect together jack terminals 7 & 8.

### **Electrical Tests**

The test for distance unit is accomplished by use of test connections shown in Fig. 16. Tripping is indicated by a voltmeter reading connected to the output terminals. At the balance point, the voltmeter reading may be as low as 1 volt or 2 volts d.c. indicatingthat the system is only tripping during a part of a cycle. This is normal balance point characteristic; however, an increase in current over 5 per cent should produce output of 15 to 21 volts d.c. A reading less than 12 volts indicates a defective tripping output. When checking current and voltage limits allow for additional instrumentation errors.

Set relay for all T == 10.0

Step 1. Monitor output #1 at Varicon terminals

"5" and output #2 at Varicon terminals

"6". Apply 40 volts ac to Varicon terminals

"7" and "8" with polarity mark on

terminal "7" apply a-c current into current terminal "5" out current terminal

"7" (jumper terminals "8" and "6" together).

Apply rated d-c voltage to Varicon terminals "4" and "3" with positive on "4".

- a) Set phase shifter at 40° current lagging voltage. The trip current should be between 1.11-1.19 amps.

- b) Set phase shifter for  $290^{\circ}$  current lagging voltage. The trip current should be 1.12-1.18 amps.

- Step 2. Reverse current connections to terminals "5" and "7". Repeat step 1, monitoring output #1 and #2.

- Step 3. Set phase shifter for 345° current lagging voltage. Monitor outputs #1 and #2. Relay should operate between 1.92 and 2.12 amperes.

- Step 4. Move current lead from terminal "7" to terminal "6". Tripping current on both units should be between 3.84-4.24 amp.

- Step 5. Reconnect current circuit with current into terminal "5" out terminal "7" ("6" and "8" jumpered). Set voltage for 125 volts a.c., current 75° lagging. Check outputs #1 and #2 operating current should be below 0.400 amp. at some point between 73° and 78°.

- Step 6. Reverse current connections to terminals "5" and "7" and repeat Step 5.

If some other T-setting than T=10 is used for testing the current values should be obtained by using following equation.

$I_{test} = \frac{V}{2T} \cos{(15 + \text{c})} \; (\pm \; 4\%) \; \text{ where c, is angle by}$  which current lags the voltage.

If the electrical response is radically outside the limits after making allowance for instrumentation error (particularly the phase angle meter error is of critical importance). Relay should be recalibrated as outlined in the section under "Calibration Procedure."

### ROUTINE MAINTENANCE

The relays should be inspected periodically, at such time intervals as may be dictated by experience, to insure that the relays have retained their calibration and are in proper operating condition.

### REPAIR CALIBRATION

Use the following procedure for calibrating the the relay if the relay has been taken apart for repairs or the adjustments disturbed. For best results in checking calibration the relay should be allowed to warm up for approximately one hour at rated voltage. However, a cold relay will check to within two per cent of the warm relay.

### Settings

- A. Set all compensators on T = 10.

- B. Make following potentiometer settings:

- NOTE: Loosen locknuts before rotating the brush. The locknuts should be retightened when calibration is completed.

- P2 Connect ohmmeter to the middle (brush) terminal and the free termi-

nal (without any connections), and adjust potentiometer for approximately 2000 ohms.

P1, P3, P4, P5 - Should be set in maximum clockwise position.

### **Electrical Tests and Connections**

- A. Calibrate phase shifter using wattmeter method of  $90^{\circ}$  current lagging voltage for 0-watts reading, and at  $60^{\circ}$ . The watts at  $60^{\circ}$  should read one-half of the maximum watts reading obtained on the wattmeter at  $0^{\circ}$  setting.

- B. Output from unit #1 is observed between varicon terminals #5 and #3, and for output from unit #2 between Varicon terminals #6 and #3. Monitor relay output using high impedance (at least 20,000 ohms/volt) d-c voltmeter suitable for reading 0-25 volts d-c. Consider as positive relay output voltmeter deflection of 5 volts or more. Then, increase current slightly beyond the limits for full 18-20 volts d-c output.

- C. Apply a-c voltage to Varicon terminals "7" and "8" with polarity mark on terminal "7."

- D. Apply a-c current into current terminal "5" out current terminal "7" (jumper terminals "8" and "6" together).

- E. Apply rated d-c voltage to Varicon terminals "4" and "3," with positive on "4".

### RELAY CALIBRATION

- A. Apply 40 volts a-c and 1.15 amp. of a-c current. Set phase shifter at 40° current lagging voltage. Adjust P1 until output #1 is first obtained, and then just resets.

- B. Set phase shifter for 290° current lagging voltage. Set current for 1.15 amp. and voltage for 40 volts a-c. Adjust P2 until an indication of output #1 is obtained.

- C. Repeat step A.

- D. Recheck step B: If P2 adjustment was needed, then recheck step A; if no P2 adjustment was

needed, lock P1 and P2. If P1 adjustment was needed repeat step B. In general, repeat steps A and B again until P1 and P2 readjustments are not needed. Lock P1 and P2.

- E. Monitor output #2. Adjust P4 until trip current is 1.12-1.15 for 40 volts a-c at  $40^{\circ}$  and  $290^{\circ}$  current lagging.

- F. Reserve current connection to terminals "5" and "7" and repeat step E. Adjust P5 to meet limits.

- G. Monitor output #1. Adjust P3 until trip current is 1.15 amp. at  $40^{\circ}$  current lagging and 1.15 amp. at  $290^{\circ}$  (±1°) current lagging.

- H. Set phase shifter for 345° current lagging 40 volts a-c. Check outputs #1 and #2. Current limits should be 1.94-2.10 amps. Apply current into terminal "5" out "6" only. Check outputs #1 and #2. Current limits should be 3.88-4.20 amperes.

Apply current to terminals "8" and "7" only with polarity on "8". Check outputs #1 and #2. Current limits should be 3.88-4.20 amperes.

- I. Connect current again into term. "5" out terminal "7" (terminals "8" and "6" should be jumpered together). Set phase shifter for 75° current lagging 120 volts A-C. Check outputs #1 and #2. Operating current should be below .400 amps. between 73° and 78°.

- J. Set phase shifter for  $165^{\circ}$  current lagging, and repeat step "H."

- K. Set phase shifter for 255° current lagging 120 volts a-c. Check outputs #1 and #2. Operating current should be below .400 amps between 255° and 257°.

### RENEWAL PARTS

Repair work can be done most satisfactorily at the factory. However, interchangeable parts can be furnished to the customers who are equipped for doing repair work. When ordering parts, always give the complete nameplate data. For components mounted on the printed circuit board, give the circuit symbol, electrical value and style number.

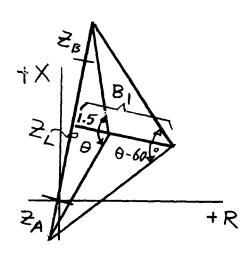

APPENDIX I — Determination of Outer Blinder Setting with Inner Blinder Set for 0.104 (ZA + ZL + ZB)

$$\theta = 2 \tan^{-1} \frac{0.5}{0.104} = 2 \tan^{-1} 4.8$$

$$\theta = 2 (78.2) = 156.4^{\circ}$$

With a  $20^{\circ}$  per cycle swing rate and a 50 milliseconds logic criterion, the limiting swing angle between blinder operations is  $20 \times 3 = 60$  degrees.

$$\frac{\theta - 60}{2} = \frac{156.4 - 60}{2} = 48.15^{\circ}$$

$$B_1 = \frac{Z_A + Z_L + Z_B}{2 \tan 48.15^{\circ}} = 0.448 (Z_A + Z_L + Z_B)$$

Use

$$Z_{outer} = 0.5 (Z_A + Z_L + Z_B)$$

This is the minimum setting of the outer blinder for 20 degree per cycle swing rate.

### APPENDIX II - Determination of Outer Blinder Setting with Inner Blinder Set for 1.5 Ohms.

At 20 degrees cycle swing rate and 50 millisecond logic criterion the limiting swing angle between blinder operations is  $20 \times 3 = 60$  degrees.

Defining

$$Z_T = Z_A + Z_L + Z_B$$

$$\tan \left( \frac{\theta - 60}{2} \right) = \frac{Z_{\rm T}}{2B_1}$$

$$B_1 = \frac{Z_T}{2} \left[ \frac{1}{\tan (\theta/2 - 30)} \right]$$

$$B_1 = \frac{Z_T}{2} \left[ \frac{1 + \tan \theta / 2 \tan 30}{\tan \theta / 2 - \tan 30} \right]$$

$$B_1 = \frac{Z_T}{2} \left[ \frac{1 + 0.577 \tan 0/2}{\tan \theta/2 - 0.577} \right]$$

$$B_1 = \frac{Z_T}{2} \left[ \frac{\sqrt{3} + \tan \theta/2}{\sqrt{3} \tan \theta/2 - 1} \right]$$

but

$$\tan \theta/2 = \frac{Z_T}{2(1.5)} = Z_T/6$$

then:

$$B_{1} = \frac{Z_{T}}{2} \left[ \frac{\sqrt{3} + Z_{T}^{3}}{Z_{T} / \sqrt{3} + 1} \right]$$

Use  $Z_{outer} = 1.1 B_1$

$$Z_{\text{outer}} = 0.55 Z_{\text{T}} \left[ \frac{\sqrt{3Z_{\text{T}}} + 9}{3Z_{\text{T}} - 3 \sqrt{3}} \right]$$

This is the minimum setting of the outer blinder for 20 degree per cycle swing rate.

### TABLE I

# NOMENCLATURE FOR RELAY Type SDBU-2

### ITEM

## DESCRIPTION

S#14C9400H21

CA1 1.1 Mfd. Capacitor

CA2, CA3, CA4, CA5 0.6 Mfd. Capacitor

Zener Regulating Diode 1N2984B

### PRINTED CIRCUIT BOARDS

DZP

| Operating Board       | S# 899C632G01       | Fig. 10 |

|-----------------------|---------------------|---------|

| Polarizing Board "+1" | 899C633G01          | Fig. 11 |

| Polarizing Board "-1" | 899C634G01          | Fig. 12 |

| Polarizing Board "+2" | 899C635G01          | Fig. 13 |

| Polarizing Board "-2" | 899C636G01          | Fig. 14 |

| Output Board          | 899C63 <b>7</b> G01 | Fig. 15 |

### **RHEOSTATS**

| PI             | 25 Watts, 5000 Ohms | S# 836A635H06 |

|----------------|---------------------|---------------|

| P2, P3, P4, P5 | 25 Watts, 5000 Ohms | 836A635H02    |

### **RESISTORS**

| $R_{DC}$                                                                                                                          | 48V dc 40W 400 Ohms         | S# 1955579 |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------|

|                                                                                                                                   | 125 V dc 40W 1500 Ohms      | 1955 645   |

| R <sub>1A</sub> , R <sub>2A</sub> , R <sub>3A</sub> , R <sub>4A</sub> , R <sub>5A</sub>                                           | 25 Watts, 2129 Ohms         | 1210089    |

| $x_{A2}$ , $x_{A3}$ , $x_{A4}$ , $x_{A5}$                                                                                         | Phase Shifting Transformers |            |

| $\begin{bmatrix} I_{pol}, & +T_{A1}, & +T_{B1}, & -T_{A1}, & -T_{B1} \\ & +T_{A2}, & +T_{B2}, & -T_{A2}, & -T_{B2} \end{bmatrix}$ | Compensators Assembly       |            |

| T <sub>1</sub> , T <sub>2</sub> , T <sub>3</sub> , T <sub>4</sub> , T <sub>5</sub>                                                | Coupling Transformers       |            |

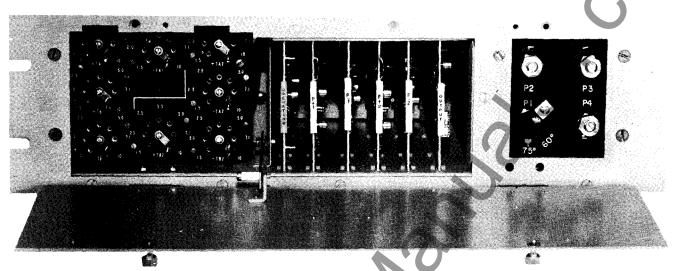

Fig. 1. Photograph of the Relay

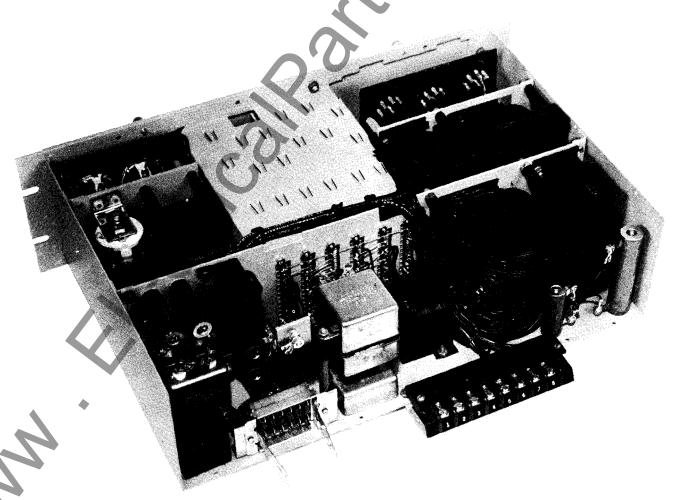

Fig. 2. 1 with Cover Off (Rear View)

Fig. 3 2 with Cover On (Front View)

REVERSE REACH (-TAL & TBL)

REVERSE REACH (-TAL & TBL)

REVERSE REACH (+TAL & TBL)

REVERSE REACH (+TAL & TBL)

FORWARD REACH (+TAL & TBL)

FORWARD REACH (+TAL & TBL)

RESTRAINT SIDE

876A578

Fig. 5 Compensator Construction

Fig. 6 SDBU-2 Relay R-X Diagram Characteristics

671B600

Fig. 7 SDBU-2 Phasor Relationship for Selected Conditions

Fig. 8 Impedance Characteristics

Fig. 11. Polarizing Board "+1"

Fig. 12. Polarizing Board "-1"

Fig. 13. Polarizing Board "+2"

D32

D31

012

R31

R30

R34

R35

D44

D43

**Z36**

**Z** 3

QS4

671B647

Fig. 14. Polarizing Board "-2"

Fig. 15. Output Board

Fig. 16. Test Connections for SDBU-2 Relay

Fig. 17. Case Outline

MAN CORE

MAN CORE CORE

WESTINGHOUSE ELECTRIC CORPORATION RELAY-INSTRUMENT DIVISION NEWARK, N. J.

Printed in U.S.A.