## INPUT ISOLATION BOARD

## S#1640A29

## INTRODUCTION

This card contains six circuits, each of which serves as an attenuator, isolator and filter for coupling external high level logic signals into 5 or 15 volt controllers. The input signals are the presence or absence of some defined AC or DC voltage. These signals usually indicate an open or closed contact on some external device.

Table 1 shows the input voltages which can be used with the different styles of this card, as well as the logic type into which each style interfaces. The operate times for each style are also given.

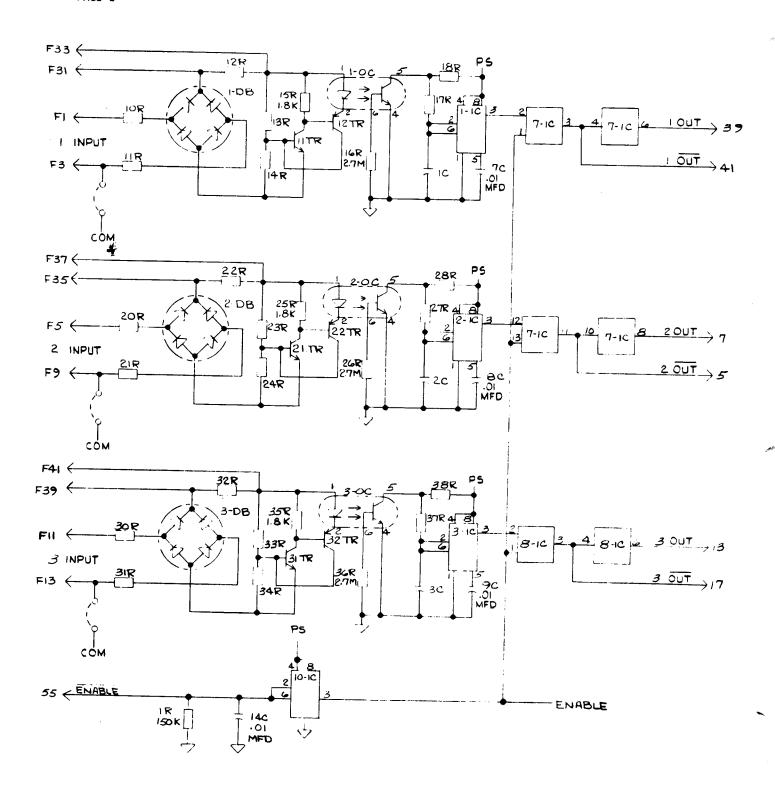

FIG. 2(a)

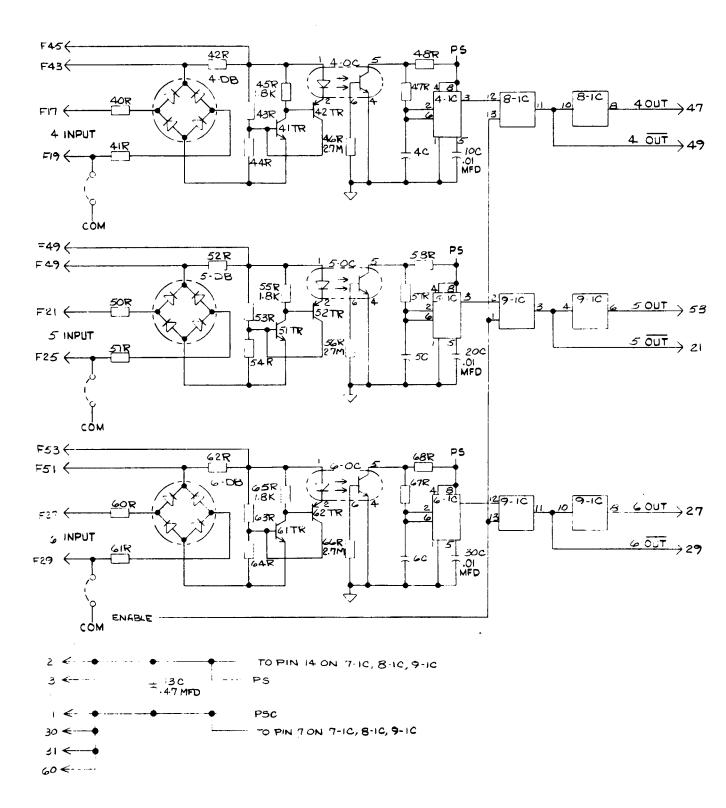

FIG. 2(b)

# II. APPLICATION INFORMATION

| ,        | INPUT VOLTAGE | LOGIC POWER | OPERAT<br>(MILLISECON | OPERATE TIMES (MILLISECONDS, TYPICAL) | ONE SIDE OF INPUTS | INPUT        |

|----------|---------------|-------------|-----------------------|---------------------------------------|--------------------|--------------|

| 3        |               |             | - CAD                 | DROPUDI                               | CUNNECTED TOGETHER | CURRENT (ma) |

| <u>.</u> | 110 VAC ±25%  | 5 VDC ±10%  | 8 - 8                 | 11 - 15                               | No                 | 8 ±25%       |

|          | 110 VDC ±20%  |             | 4                     | 15                                    |                    | 8 ±20%       |

| 602      | 20 - 60 VDC   | 5 VDC ±10%  | 0.7                   | 1.2                                   | No                 | 4 - 15       |

| 603      | 110 VAC ±25%  | 12 - 16 VDC | 4 - 8                 | 11 - 15                               | No                 | 8 ±25%       |

|          | 110 VDC ±20%  |             | 4                     | 15                                    |                    | 8 ±25%       |

| 604      | 11 - 28 VDC   | 5 VDC ±10%  | 7.0                   | 1.2                                   | No                 | 6 - 21       |

| 905      | 20 - 50 VAC   | 5 VDC ±10%  | 4 - 8                 | 11 - 15                               | ON                 | 4 - 13       |

|          | 20 - 60 VDC   |             | 4                     | 15                                    |                    | 4 - 15       |

| 909      | 20 - 50 VDC   | 12 - 16 VDC | 8 - 8                 | 11 - 15                               | No                 | 4 - 13       |

|          | 20 - 60 VDC   |             | 4                     | 15                                    |                    | 4 - 15       |

| 200      | 20 - 60 VDC   | 12 - 16 VDC | 0.7                   | 1.2                                   | No                 | 4 - 15       |

| 809      | 110 VAC ±25%  | 5 VDC ±10%  | 4 - 8                 | 11 - 15                               | Yes                | 8 ±25%       |

|          | 110 VDC ±20%  |             | 4                     | 15                                    |                    | 8 ±20%       |

| 609      | 110 VAC ±25%  | 15 VDC ±10% | 4 - 8                 | 11 - 15                               | Yes                | 8 ±25%       |

|          | 110 VDC ±20%  |             | 4                     | 15                                    |                    | 8 ±20%       |

|          |               |             |                       |                                       |                    |              |

TABLE 1

When an input voltage within the defined voltage range is present at the input terminals, the OUT terminal is a LOGIC 1 (high level) and the OUT terminal is a LOGIC 0 (low level). If the input voltage is not present, or if the ENABLE input is at a LOGIC 1, or both, then the OUT terminal is a LOGIC 0 and the OUT terminal is a LOGIC 1 below.

The circuit ignores all input voltages below a threshold level, typically 1/2 of the nominal input

Power Supply Current: GO1, GO2, GO4, GO5, GO8:

$5VDC \pm 40 ma$

(typical)

G03, G06, G07

$15VDC \pm 100 ma$ .

Logic Loading: Each OUT terminal will drive 8 logic loads.

Each OUT terminal will drive 7 logic loads.

The ENABLE input should be considered 1 logic load. If left unconnected, this input assumes the low (LOGIC 0) state.

The above logic loads refer to DTL loads(5volt logic) or HTL loads (15 volt logic).

The inputs card can also be used to interface with CMOS circuits.

Logic Level Definitions:

| <u> </u>                       | 01,G02,G04,G05, | G03,G06,G07 |      |    |        |

|--------------------------------|-----------------|-------------|------|----|--------|

| A logic 1 state is defined as: | +5.5V to        | +2.6V       | +16V | to | +12.5V |

| A logic O state is defined as: | 0.0V to         | +0.5V       | 0.0V | to | +1.50  |

#### III. DESCRIPTION OF OPERATION

Refer to the first of the six inputs shown in the scheme (top of Figure 2(a)).

In order to get a LOGIC 1 signal on the 1 OUT terminal 39, a voltage as defined in Table 1 must be applied across the INPUT terminals F1 and F3 (terminals with F prefixes are located on the front edge of the board, away from the backplane). If the applied input is an AC voltage, the signal is rectified by the diode bridge 1-DB. A visible light-emitting diode (VLED) is typically connected between terminals 31 and 33, anode on 31, and the rectified input current (as limited by resistors 10R and 11R) flows through the VLED, through 12R and through the voltage divider 13R and 14R. Whenever sufficient current flows to raise the voltage across 14R to approximately 0.6 volts, 11TR turns on which turns on 12TR and causes current to flow in the infra-red light-emitting diode (IR LED) of the coupler. Current flowing in the IR LED causes the phototransistor to conduct current, which discharges capacitor 1C through 17R. When the voltage across 1C drops to 1.7 volts, the output of timer 1-IC (pin 3) rises to a high state, giving a LOGIC 0 output on terminal 41  $\overline{(1\ 001)}$  and a LOGIC 1 output on terminal 39 (1 OUT). With AC inputs, current in the optical coupler is derived from the rectified but unfiltered sine-wave input voltage. The current in the photoransistor is therefore pulsing at 120 hz (for 60 hz inputs). During the time when current in the phototransistor is off, 1C begins to charge. But the charging time constant  $T = (17R + 18R) \times 1C$  is approximately 10msec., so the capacitor does not charge to a very high voltage before it is discharged again through the phototransistor at the next half-cycle of the input current. Only when the input voltage is removed does 1C charge to the 3.4 volt threshold voltage of the timer 1-IC. At this time the outputs change back to their initial states. The capacitor stays charged to about 4 to 5 VDC until the next time the input voltage is present.

When the ENABLE input is driven to the LOGIC 1 state, all six circuits are inhibited so that the OUT terminals become LOGIC 0 and the  $\overline{ ext{OUT}}$  terminals become LOGIC 1, regardless of the presence or absence of voltage on the individual inputs.

## IV. SERVICE

Personnel familiar with electrical equipment utilizing semiconductors can isolate most problems using an oscilloscope, multimeter, and information contained in relative instruction leaflets.

Semi-automatic equipment is available at the factory to test static and dynamic performance of all edge-connected, printed circuit boards. Generally, repair of boards is facilitated by returning them to:

Westinghouse Electric Corporation Industrial Equipment Division P. O. Box 225 Buffalo, New York 14240

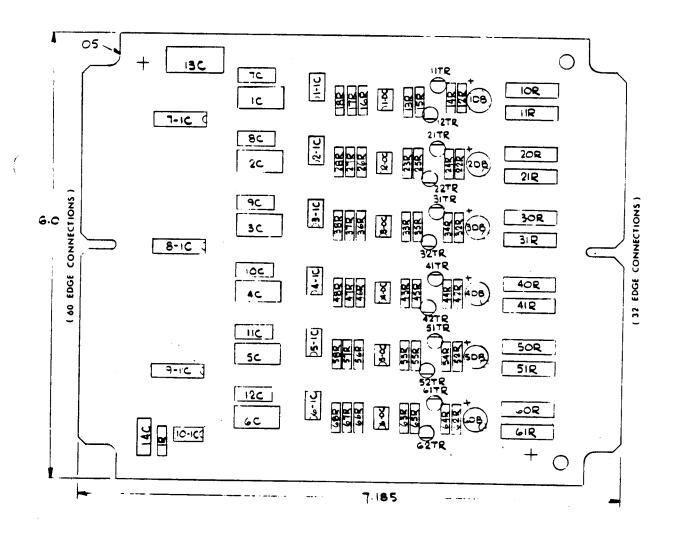

FIGURE 4