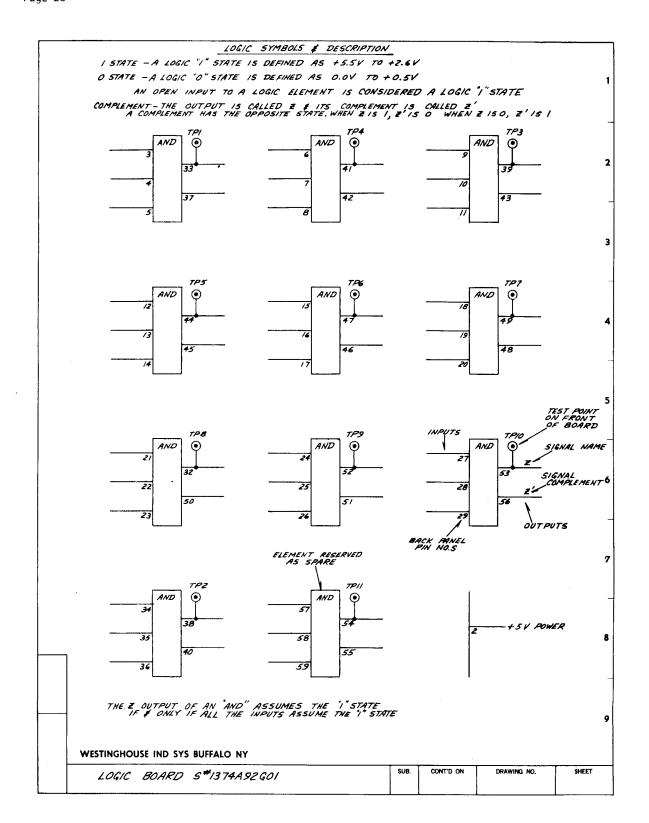

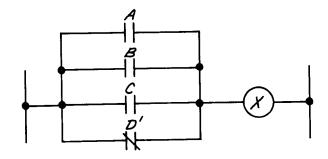

FIGURE 1

QB/11 PLUS PROGRAMMABLE CONTROLLER

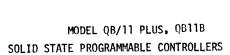

Figure 2

QB11B PROGRAMMABLE CONTROLLER

#### INDEX

- I. INTRODUCTION

- II. APPLICATION

- III. DESCRIPTION OF APPARATUS

- IV. PROGRAMMING PROCEDURE

- V. START-UP PROCEDURE

- VI. REFERENCES

- VII. APPENDIX

### INTRODUCTION

This controller is the standard QUARTERBACK Model 11 Programmable Controller. Normally, the con.roller (often called the Model QB/11 requires only four types of circuit boards --input isolation boards, output Triac boards, logic boards, and timers. The controller is programmed using convenient English language logic statements. The program is compiled off-line and the results reside in the backplane wiring of the controller. Figure 1 depicts the QB11+ and Figure 2 depicts the QB11B.

## II. APPLICATION

The QB/11 is designed as an economical replacement for relay systems having approximately 50 to 100 relays for QB11+, 50 to 200 relays for QB11B. QB11B is the preferred design with application of QB11+ reserved for those applications where rear access is not available.

# III. DESCRIPTION OF APPARATUS

The QB11+ consists of 2 power supplies, 2 two-row assemblies, incoming-line circuit breaker, terminal blocks, and interconnecting wiring -- all factory assembled in a dust-tight enclosure, Figure 1. Note that the input and output boards are located toward the left hand side of the enclosure. Normally, inputs are in the top cage assembly and outputs are in the bottom cage assembly, although they can be inter-mixed if necessary.

The QB11B consists of a single power supply, a 5 row cage assembly, incoming line circuit breaker, terminal blocks and interconnecting wiring — in a dust — tight enclosure, The input and output boards are located in the top and bottom row of the cage assembly, additional I/O boards are allocated to the adjacent rows.

The size of QB/11 is determined primarily by the number of inputs and outputs. Although the only way to determine the exact number of logic boards is to program the controller, a very accurate estimate can be made for relay type circuits by adding the number of input boards to the number of output boards and dividing by two. The maximum number of input plus output boards that can be accommodated is 40 for QB11+, 64 for QB11B each input board can accommodate 6 inputs and each output board can accommodate 4 outputs.

In a QB11+ a maximum of 64 total boards can be accommodated plus an additional four outrigger boards for the power supplies.

In a QB11B a maximum of 135 boards can be accommodated, one of which is allocated for the power supply sequencer board.

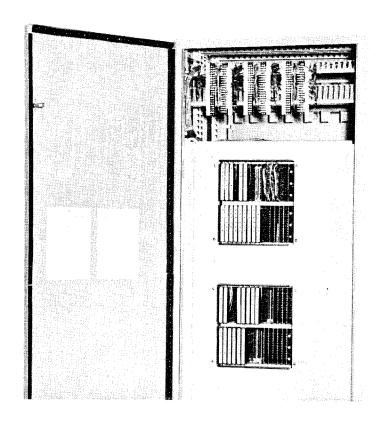

FIGURE 3

Indicating lights are provided on each input and output. Figure 3. The indicating lights are on the front of the input and output boards with the corresponding signal names printed by the computer program on sheets which are placed in plastic envelopes on the inside of the front door.

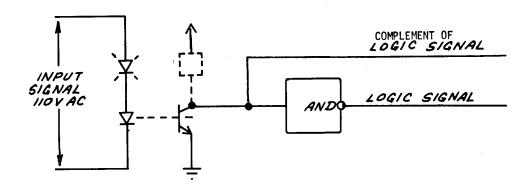

The input isolation board receives six 110-volt input signals, each of which drives two LED's, Figure 4. One LED provides visual indication of input status, and the other isolates the 110-volt signal from the five-volt logic. The signal from the LED is filtered and amplified to provide the input signal and its complement.

FIGURE 4

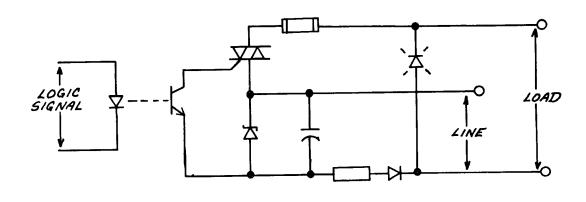

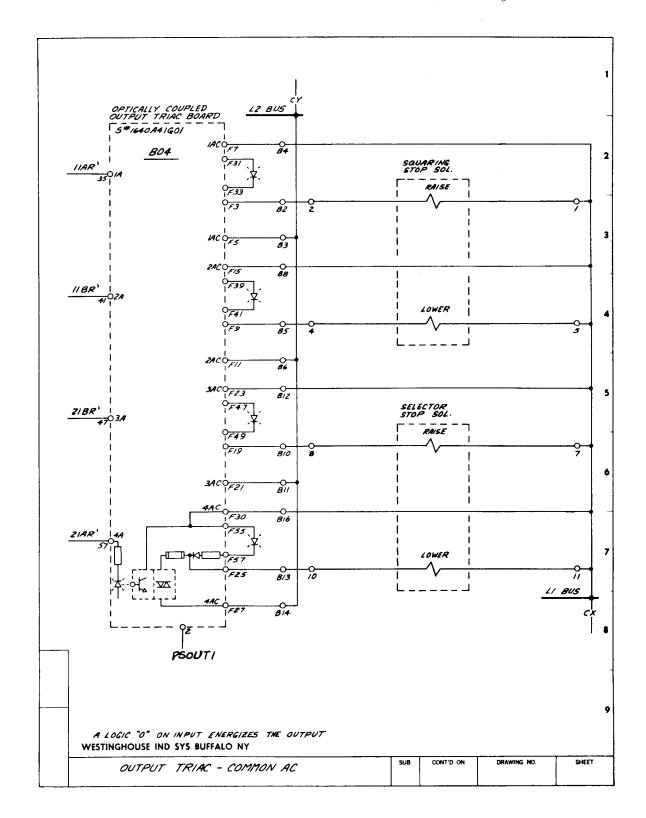

The 110-volt output board contains four triac circuits, each having a LED and photo-transistor for isolation, Figure 5. A separate LED provides visual indication of output status. The Triac output is rated for 1.5 amperes continuous current and 10 amperes inrush current. A slow-blow fuse rated 3 amperes is provided on the output board for one side of the line. For a full description, ratings and characteristics, refer to Output Board I.L. 16-800-258.

FIGURE 5

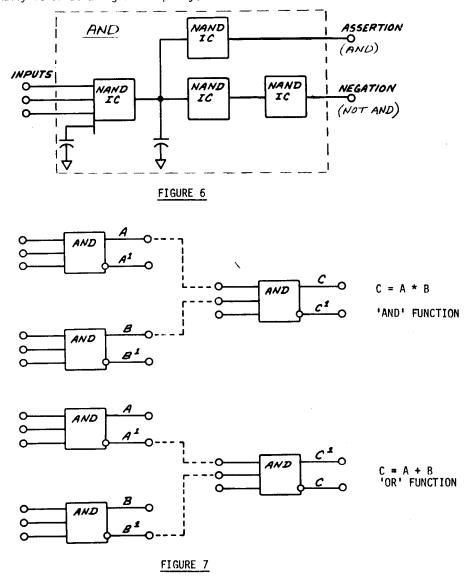

The logic board contains 11 three-input AND elements. Figure 6. Both the assertion and complement outpusignals are available, as are test points on the front of the board. Each "AND" element can drive 8 additional loads. Since the complement of all signals is always available in the controller, the logic element is as efficient in producing the OR function as it is in producing the AND function, Figure 7.

The AND elements are actually composed of for integrated circuit NAND elements. This allows capacitors to be inserted to sedate the logic against loise. The circuit provides a pulse width cut-off point of 20 microseconds, which effectively shields the OB/II from electrical noise problems that normally occur at a higher frequency.

Additional output boards are av ilable for special functions. The digital to-analog converter board is especially useful for providing speed reference ignals to variable speed drives. A mercury-wetted relay output loard is also evailable for special functions and to send monitoring information to a remote computer.

An automatic start circuit is provided to initialize seal-in circuits in the "off" position. It is very important that the engineer designing a QB/1 Plus is familiar with this feature. Basically, it a seal is circuit is unit ated with a normally oper contact and the seal-in circuit is broken with a normally closed circuit is broken with a normally closed circuit is broken with a normally cosed circuit is broken with a normally cosed circuit is broken with a normally closed circuit is broken with a accomplished by delating input situals a sime delay after first applied to the controller. This appears to the control that a normally closed circuit that been open thus breaking the seal-in Outp the power is of corrected and until input power is applied and the logic stable. The sequence is automatically a plied when power is applied. For a full description, ratings and characteristics, refer to Sequencer Board I.L. 16-800-259.

Perhaps the most important feature of the QB/11 is the computer-aided design package. The program includes a compiler and a simulation program. Both programs run on the Westinghouse computer at Buffalo. For details on these functions see section on Programming.

### IV. PROGRAMMING PROCEDURE

### Generation of Equations

The QB-11 is programmed from sets of equations. The equations de cribe the switching functions to be performed. Each equation is a shorthand statement that specifies the conditions which must exist for liven s g all to assume the logical value of 'l' to be "turned on". An analogous s tuation is the relay 'adder diagram. Each "rung" of the diagram corresponds to an equation the contact arrangements determine the signal conditions that must exist for the relays to be energized.

The equations involve only the log cal concepts of "AND", "OR", and "NOT", so, even though they are written using certain prescribed symbols, their generation is straight forward. The igna corresponding to the relay to be energized is written on the left hand side of the equal sign. The signal onditions which must be satisfied, eg. the relay contact configuration, is written on the right hand side of the equal sign. The symbols used are as follows.

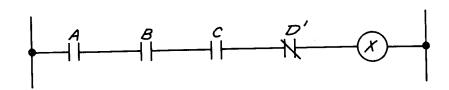

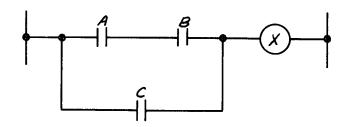

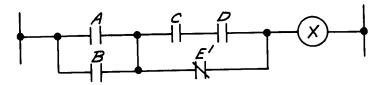

AND (\*) The logical "AND" operation in relay circuitry is represented by a series contact string:

In equation format this is written as the expression:

$$X = A * B * C * D$$

$\overline{\text{OR}}$  (+) The logical "OR" operation in relay circuitry is represented by a group of parallel contacts:

which in equation format becomes the expression

$$X = A + B + C + D^{\bullet}$$

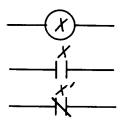

NOT (') The logical negation operation in relay circuits is usually represented by normally-closed contacts. If relay  $\underline{X}$  is energized, a normally-closed contact associated with the relay generated the complementary signal.

(The normally-open contact represents the actual signal.) In the equation format the logical negation is written:

X'----The complementary signal or logical negation.

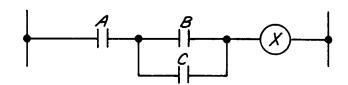

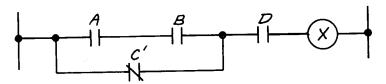

<u>Parentheses ()</u> Sets of contacts which effectively become one signal are handled by parenthetical groupings when written as equations. For instance

is written in equation format as:

$$X = (A * B) + C.$$

The expression

$$X = A * (B + C)$$

is logically equivalent to the contact arrangement

Parentheses should be used as necessary to clarify the designer's intent.

Multiple sets of parentheses may be used as required. For example:

is written:

$$X = (A+B) * ((C * D) + E')$$

In simple cases an equation may be written directly from a normal language statement of the function to be performed. However, until proficiency is developed in handling the equations, the design of more involved circuits can be accomplished in two steps; first by drawing "relay-oriented" schematic, and then by making a "coi -by-coil" conversion from the relay circuit to the equations. As an example of this proceedure consider the following. In English, a ircuit is to operate as follows:

"Relay X will be energized if contact D is closed--if signal D is present--and if either (a) contact A and contact B are both closed, or (b) if 'normally-closed' contact C' is closed, or (c) if both of the above conditions prevail".

As a "rung" of a relay circuit diagram this becomes:

In equation form it is written

$$X = ((A * B) + C^{\dagger}) * D$$

# 2. Additional Features

Additional features to be incorporated into the QB-11 circuitry are specified by certain prefixes added to the equations. The following sections on Timers and Outputs require prefixes.

a) Two types of timer boards are available, the Extended Range Timer, and the Single Shot Timer. These are programmed by prefixing (TMxxx) and (TIMEF or TIMEV) respectively to the appropriate logic statement. The type of board required for a particular time range is as follows:

# Extended Range Timer (TMxxx)

S#1640A45G01 - 3 per board 1 sec. to 40 min. S#1640A45G02 - 3 per board 1 sec. to 40 sec.

# Single Shot Timer (TIMEF or TIMEV)

S#1594A16G01 - 2 per board .15 sec. to .75 sec. (TIMEF)

3 per board .65 sec. to 3 sec. (TIMEV)

An example of two equations using an Extended Range Timer follows:

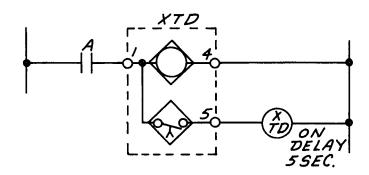

#### Time Delay On

If it is desired that the signal generated by the equation (left hand side) appear only after a time has elapsed, the prefix  $\underline{\text{TMxxx}}$  is used. In the figure below if "XTD" is to become '1' 5 seconds after A has become '1'. This

is written in equation format as:

TM005 XTD = A

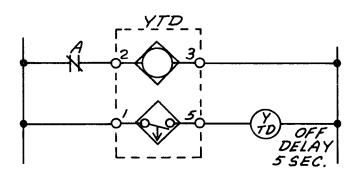

## Time Delay Off

If a signal should remain "on" for a period of time after the conditions causing it have disappeared, the same prefix is used with complemented functions. This

is written in equation format as:

TM005 YTD' = A'

indicates that the signal YTD is to remain a 'l' for 5 seconds after the value of A' goes from a 'l' to a 'O'.

## b. Outputs

Two types of output devices are available, the AC switch (TRIAC), and the Hg-wetted relay. These are programmed by prefixing OUTT and OUTR respectively to the appropriate logic statement. If, for instance, Solenoid 1 is to be energized by a TRIAC when Limit Switch 1 closes if either Selector Switch 1 is closed or the system is in "auto", is written as

The expression indicates that not only is signal SOL1 to be generated, but also that it is to drive an output TRIAC.

#### 3. PROGRAMMING FORMATS

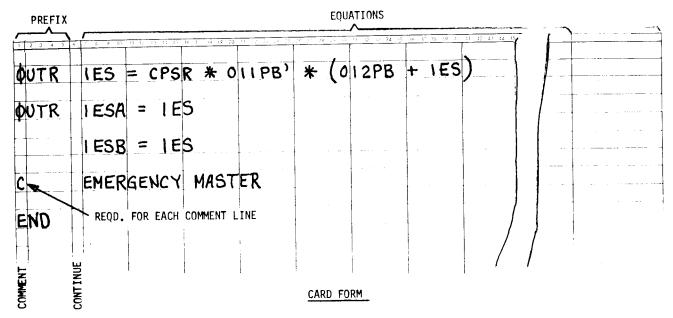

### a. Equation Formats

The programming of the QB-11 is facilitated by using a standard card form with 80 columns. All prefixes begin in column 1 and all equations begin in column 7. Equations can not be written beyond column 72. If an equation's length exceeds the column 72 limitation, it may be "continued" by putting the symbol & in column 6 of the next line and continuing in column 7. Up to 9 continuation lines may be used for a given equation.

Blanks may be used for clarity in writing the equation; however, they should  $\underline{not}$  be inserted in symbol names. Symbol names may be up to seven characters long, either alphabetic, or numeric, or both.

The letter C in column 1 followed by five blanks, (a skip to column 7) indicates that the remainder of the line is a "comment" and not to be processed by the programming system. Comments provide an excellent method of annotating the system logic. Their use is highly recommended. Comments may not appear between the lines of, "continued" equations. However, as many comment lines as necessary may be used.

The end of the set of equations is indicated by the word END beginning in column 1.

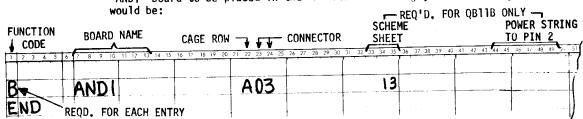

## b. Cage Layout

The exact cage layout must be specified for each QB-11. This layout is given in a list which makes a one-to-one association between the available printed circuit boards and the cage connectors. The list is prepared on a standard card form. To cause a "AND1" board to be placed in the 'A' row of the cage, connector 03, the list entry would be:

Any "slot" omitted from the list will be assumed to have no connector in it. Any signal assigned to an empty slot will cause the programming system to reject the design.

The available printed circuit boards are:

|                                                    |       | BOARD N | IAME QB11+ | <u>-</u> | BOARD NAME QB11B |

|----------------------------------------------------|-------|---------|------------|----------|------------------|

| BOARD DESCRIPTION                                  | ROW A | ROW B   | ROW D      | ROW E    | ANY ROW          |

| Power Supply Sequencer Power Supply Regulator      | PSQ1  | PSR1    | PSQ2       | PSR2     | PSEQ (C27)       |

| Optical Coupled Input                              | LDN1  | LDN2    | LDN1       | LDN2     | LDN              |

| Logic                                              | ANDT  | AND2    | AND3       | AND4     | AND              |

| Extended Range Timer                               | TMR1  | TMR2    | TMR3       | TMR4     | TMR              |

| (3 @ 1.0 sec. to 40 sec. or                        |       |         |            |          |                  |

| 3 @ 1.0 sec. to 40 min.) Single Shot Timer         | TIME  | TIME    | TIME       | TIME     | TIM              |

| (2 0 .15 sec. to .75 sec. & 3 0 .65 sec. to 3 sec. |       |         |            |          | •                |

| Triac Output                                       | TRC1  | TRC2    | TRC1       | TRC2     | TRC              |

| Mercury Relay Output                               | CLR1  | CLR2    | CLR1       | CLR2     | CLR              |

| Interconnect Plug HO1 to H10                       | PLUG  | PLUG    | PLUG       | PLUG     | PLG              |

| Transmitter Bd.                                    |       |         |            |          | DIFT             |

| Receiver Bd.                                       |       |         |            |          | DIER             |

| Power Supply Plug                                  |       |         |            |          | PWRP (HO5)       |

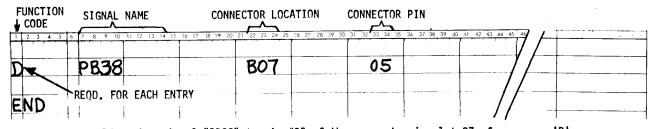

### c. Connection Specification (Optional)

A third set of data, the signal allocation list may be included if desired. This is a tabulation of signal names and their location on the printed circuit board connectors. Such a tabulation, for instance, may specify the Input/Output signals to fix the external connection locations. The preparation of this list is done on a standard card form. If the list is not included, the programming system will automatically supply its own assign ments (alphanumerically). In most situations this is quite adequate. Input/Output signals may be manually assigned in total or selectively.

The formatted line:

would assign signal "PB38" to pin #05 of the connector in slot 07 of cage row 'B'.

It is necessary to know in advance exactly which pins of each individual connector are available for use, and to know exactly how the circuitry of the various printed circuit boards is arranged. It is also necessary that the layout of the cage be known(see Section 3b CAGE LAYOUT).

Whether the list is included or not, the word  $\underline{END}$  must be coded beginning in column 1. If there is no list, two lines beginning  $\underline{END}$  would appear in succession (because of the  $\underline{END}$  terminating the cage layout list).

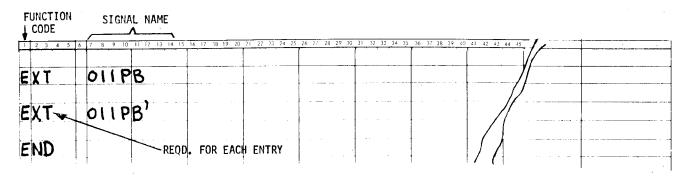

## External Signals (Optional)

All signals which are not generated by the logic (i.e. do not appear on the left hand side of an equation) must be brought in from the "out side". This may be done in either of two ways: automatically by the computer identifying and assigning the input signal(s) or manually by specifying the signal(s) in question to be an EXT signal.

Incoming signals specified automatically by the computer are always assigned with the unprimed signal name assigned to the direct (Z) output of the input board; the primed signal name is assigned to the complementary (Z') output of the input board. If it is necessary to reverse this signal assignment two things must be done: suppress the automatic generation of the input signal by specifying the signal as an EXT signal and "manually" assigning the signal to the desired connector pin in the manual assignment list.

Signals are specified as EXT signals by generating the list as

The list is terminated by END in column 1.

The EXT list, including the END card, is completely optional.

## Computer Aided Design Procedure

A OB/11 computer aided design proceedure requires several operations, which follow below in a step by step order.

# Generate and Process Equations

Logic equations are generated per the Programming Procedure, Section IV. These equations are keypunched and processed thru the computer. A Pre-Processor print out is generated from which the total number of Input, Output and Logic elements required are listed. This list provides some of the information needed to generate the cage layout.

## Specify Cage Layout

When specifying the cage layout (section 3b), in addition to the board requirements determined by the pre processor, the following information is necessary.

# Power Supply Sequencer PSQ1 (A01) and PSQ2 (D01) QB11+ Always needed in position AOI (This is not on Pre-Processor) Always needed in position DOI (This is not on Pre-Processor) Power Supply Regulator PSR1 (BO1) and PSR2 (EO1)

Always needed in position BO1 (This is not on Pre-Processor) Always needed in position EO1 (This is not on Pre-Processor)

Power Supply Sequencer (C27) QB11B

Always needed in Position C27 (This is not on Pre-Processor)

## Input Relays (6 per board)

QB11+ LND1 (Row A & D) LND2 (Row B & E)

Preferred locations as follows:

| A03        | or | DO3 Input Board                 | Isolated<br>or<br>Common | Λ09<br>A10 | DO9 Input Board                 | Isolated<br>or<br>Common |

|------------|----|---------------------------------|--------------------------|------------|---------------------------------|--------------------------|

| A05<br>A06 | or | DO5 Input Board DO6 Input Board | Isolated<br>or<br>Common | A11<br>A12 | Dll Input Board Dl2 Input Board | Isolated<br>or<br>Common |

| A07        | or | DO7 Input Board DO8 Input Board | Isolated<br>or<br>Common |            |                                 |                          |

Boards shown as pairs must both be of the same type, either common AC or Isolated AC. Isolated AC should use the higher cage connectors (e.g. All, Al2, Dl1, Dl2, etc.)

QB11+ LDN (Row A & B)

Preferred locations A01 thru A26, B01 thru B12. Any  $\min$  of common and isolated AC is acceptable.

## Output Relays (6 per board) or Output Triac Boards (4 per board)

QB11+ CLR1 (Row A & D) CLR2 (Row B & E) TRC1 (Row A & D) TRC2 (Row B & E)

Preferred locations as follows:

Boards shown as pairs must both be of the same type either Common AC or Isolated AC. Isolated AC should use the higher cage connectors (e.g. B11, B12, E11, E12, etc.)

QB11B CLR, TRC (Row E)

Preferred locations EO1 to E26 with output relays near the DO1 end.

## Logic Boards (10 ANDS per board)

QB11+ AND1 (Row A) AND2 (Row B) AND3 (Row D) AND4 (Row E) Are usually located in Cage slots 13 to 18

QB11B AND (Rows A thru E)

Preferred locations positions 14 thru 26 in rows B,C,& D. Boards may be located in any position.

## Extended Range Timer (3 per board)

QB11+ TMR1 (Row A) TMR2, (Row B) TMR3, (Row D) TMR4 (Row E)

QB11B TMR (Rows A thru E)

May be located in: Any slots unused in any row.

## Single Shot Timer (5 adjustable per board) (All rows

QB11+ TIME

May be located in any slot

QB11B TIM that is unused in any row

## c. Specify "Manual" Connections List

After completing the cage layout it may be necessary to assign certain signals to particular back panel pins:

- 1. To group connections (for example, from a particular operator station customer devices, etc.) to a specific terminal block in the OB/11.

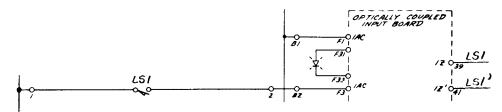

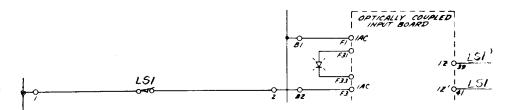

- 2. To coordinate the logic equations with the input device. For instance with the equation

RUN =

$$A * B * LSI$$

if the device which generates signal LS1 is a normally-open device and if "Run" should be a "1" if the device is not activated, then the input circuit board should be connected

If, however, the device which is to generate signal LS1 is a normally\_closed device and "Run" is still to be a "l" if the device is not activated (the same logic equation) then the input circuitry must be

The LS1 & LS1 $^3$  signals are reversed. The "inverted" assignment must be indicated in this list.

Note: Even If the Manual List is not required, an END card must be included (per section 3c).

#### d. List External Signals

A cancellation of the computers automatic input signal generation feature (section 3d) is required when signal reversal (section 4c2) is used. Both primed and unprimed signals must be listed. If no cancellations are necessary, <u>no</u> END card is used.

### 5. Simulation

Simulation is used to prove the <u>design</u> of a logic system. It is executed in much the same way a hardware test would be performed. A prescribed set of input signals are varied in a given sequence and the reaction of the logic-generated signals, described by the equations, is observed. For a full description refer to instruction leaflet on Simulation I.L.16-800-260.

THE PRECEDING SECTION HAS DISCUSSED THE PROGRAMMING PROCEDURE FOR A QB/11. FOR A SAMPLE RELAY SCHEME AND THE PROCEDURE TO CONVERT IT INTO A QB/11 CONTROLLER REFER TO THE APPENDIX, SECTION VII, OF THIS INSTRUCTION LEAFLET.

#### V. START-UP PROCEDURE

### A. <u>Introduction</u>

The QB/11 is factory checked and is assumed to be a complete, operational unit when delivered to the customer. The QB/11 should require only unpacking, mounting and external wiring.

These instructions provide a step-by-step procedure for a first time start-up of a QB/11 Programmable Controller.

The start-up procedure is recommended as a precaution against damaging any components, within or external to the QB/11.

The procedures should be followed in the specified sequence, checking each step against the schematic diagram. This will develop familiarity with the system and insure proper operation of the drive when the sequence is completed. If difficulty is encountered at any step, the source of the trouble should be determined and corrected before proceding.

Non-standard functions such as special sequencing, interconnection with other drives, etc. which pertain to a specific application are covered by separate instructions.

### B. Inspection

Check for any loose wires or assemblies. Check that all cards are firmly inserted in the slots. Check that all front connectors are firmly plugged onto the correct cards.

#### C. External Connections

- All input and output signal wiring should be connected to the terminal blocks.

These connections should be made according to the external wiring information supplied with the particular QB/11 unit.

- Before connecting the 115 VAC power input to the terminal block on the left wall of the cabinet, check that breakers 1CB and 2CB on the power panel are open (OFF). The 115 VAC 50/60 Hz power should be connected to terminals 11 and 12 of the block. Terminal 10 should be wired to plant ground.

## D. Power Supply Checks

With circuit breaker 2CB open (OFF), close circuit breaker 1CB. If the external 115 VAC supply is active, the red indicator 1IL should come on and the fan will start. With a meter, make the following voltage checks.

- 1. 115 VAC should be present between the A.C. buses feeding the input terminal block boards. The A.C. buses feeding the output boards should remain de-energized. Fuses 1FU and 2FU on the back of the power supply panel (PS2) feed the A.C. buses for the input boards.

- Check for +5VDC + 10% between pin 2 of each card connector and the common bus. (Exception: The power supply sequencer card in slots A01 and D01 on QB11+ requires no voltage on pin2.)

## E. Power Supply Sequencing Test

- Open circuit breaker 1CB and close 2CB. Connect a D. C. Voltmeter (0-10VDC) from pin 2 (positive) of any triac output card to common.

- Close circuit breaker 1CB. After approximately 8 seconds the D. C. Voltmenter reading should change from 0 volts to +5 volts D. C. and simultaneously the white light 2IL shou? come on. The A.C. buses feeding the outputs will show 115 VAC across them whenever 1CB and 2CB are both closed.

### F. Operational Tests

To simulate any actual operating situations, the following procedures may be used.

### 1.0 Input Boards

#### 1.1 Preferred Method

To simulate an input contact closure, short together the two terminals on the terminal block which connect to the external input contact being "picked up". The LED indicator will light.

#### 1.2 Alternative Method

To simulate an energized input, connect the input complement signal on the logic backpanel connectors to logic common. These signals are available for any input board \$#:640A29 on the pins shown below:

| Input Circuit | Pin No. |

|---------------|---------|

| #1            | 41      |

| #2            | 5       |

| #3            | 17      |

| #4            | 49      |

| #5            | 21      |

| #6            | 29      |

When an input contact closure is simulated on the logic backpanel by this technique, the LED indicator will not light.

### 2.0 Output Boards

2.1 To energize a triac output contact, connect the logic complement signal for that output to common by shorting the common to the pins listed below:

| Output Circuit | <u>Pin No.</u> |

|----------------|----------------|

| #1             | 35             |

| #2             | 41             |

| #3             | 47             |

| #4             | 57             |

The indicator LED will light to indicate an energized output (contact closure) if the A.C. output power is on.

### VI. REFERENCES

The following is a listing of supporting QB/11 instruction leaflets.

I.L.16-800-258 Output Triac Board

I.L.16-800-259 Power Supply Sequencer Board

I.L.16-800-260 Simulation Program

I.L.16-800-261 Extended Range Timer

## VII. APPENDIX

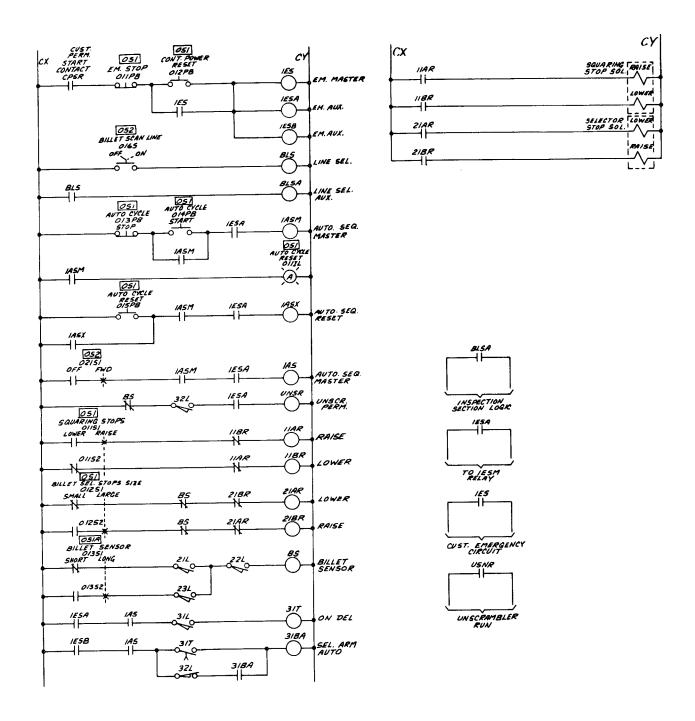

This section pertains to a sample relay schematic and the requirements needed to convert it into a QB/11 schematic.

The following circuits are part of a sample relay schematic.

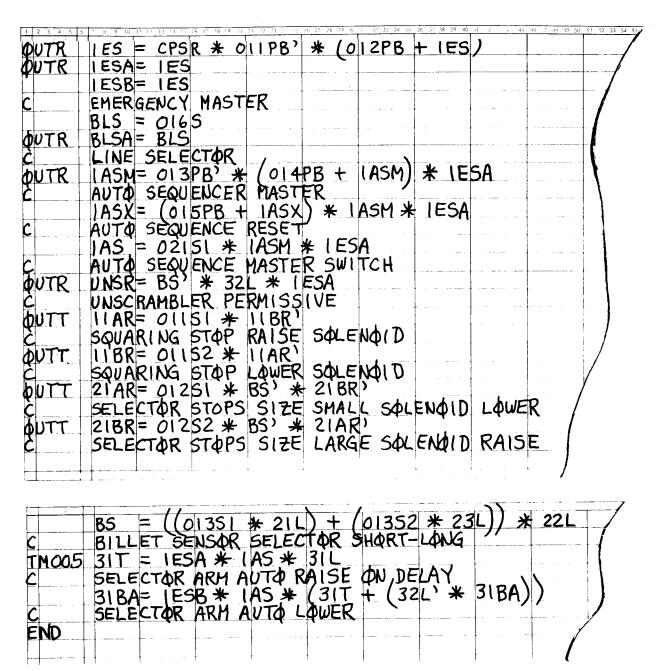

From the preceding relay schematic the following equations were written.

These equations are keypunched and processed thru the computer. The result is a Pre-Processor print out.

Following is some of the data from the Pre-Processor print-out needed to design the QB11.

## a. Specify Cage Layout

With this list and information from Cage Layout (section 4b) the total number and type of boards required are obtained. Check that 64 boards maximum are not exceeded.

#### THE NUMBER OF ELEMENTS USED ARE---

| ANDS =         | 24     |   |   | 10 | ANDS/BOARD (AND1 OR AND2) |

|----------------|--------|---|---|----|---------------------------|

| SHORT TIMERS   | =      | 0 |   | 2  | VARIABLE &                |

| LONG TIMERS    | =      | 0 |   | 3  | VARIABLE/BOARD (TIMER)    |

| TRIACS =       |        |   |   | 4  | TRIACS/BOARD (TRCL)       |

| OUTPUT RELAYS  | =      | 5 | _ | 6  | RELAYS/BOARD (CLARE)      |

| INPUT RELAYS   | 19     |   |   | 6  | INPUTS/BOARD (LEDIN)      |

| EXTENDED RANGE | TIMERS | = | 1 | 3  | TIMERS/BOARD (TIMR)       |

## b. Specify "Manual" Connections

22L

23L

31L

32L

32L \*

T

After cage layout has been completed the following options can be performed.

With the External Input Signals list and the proper input board MIC schematic, you can manually assign all the input signals (per section 4cl).

| HE FOL | LUWING SIGNALS | ARE ASSUMED TO | ВE | EXTERNAL | INPUT | SIGNALS |

|--------|----------------|----------------|----|----------|-------|---------|

| INPUT  | SIGNAL         | INPUT BUFFER   |    |          |       |         |

| NO.    | NAME           | LOADING        |    |          |       |         |

| 1      | CPSR           | 1              |    |          |       |         |

| 2      | 011PB*         | 1              |    |          |       |         |

| 3      | 01151          | 1              |    |          |       |         |

| 4      | 01152          | 1              |    |          |       |         |

| 5      | 012P8*         | 1              |    |          |       |         |

| 6      | 01251          | 1              |    |          |       |         |

| 7      | 01252          | 1              |    |          |       |         |

| 8      | 013PB*         | 1              |    |          |       |         |

| 9      | 01351          | 1              |    |          |       |         |

| 10     | 01352          | 1              |    |          |       |         |

| 11     | 014P8          | 1              |    |          |       |         |

| 12     | 015PB*         | 1              |    |          |       |         |

| 13     | 0168           | 1              |    |          |       |         |

| 14     | 02151          | ì              |    |          |       |         |

| 15     | 21L            | 1              |    |          |       |         |

|        |                |                |    |          |       |         |

16 17

18

19

20

2. With the Relay Output list and the proper output board MIC schematic you can manually assign all the output signals

RELAY OUTPUTS--NUMBER SIGNAL

1 BLSA

2 UNSR

3 1ASM

4 1ES

5 1ESA

3. With the Triac Output list and the proper output board MIC schematic you can manually assign all the output signals.

Note: The Triac Output list from the computer shows unprimed signals. In order for a Triac Board to be activated a primed signal must be used. Since the Logic boards produce both primed and umprimed signals, you must use the complementary signal from that in this list.

TRIAC OUTPUTS--NUMBER SIGNAL

1 11AF .

2 11BR .

3 21AR .

4 21BR

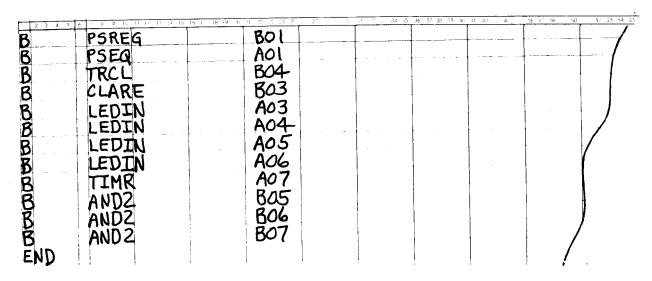

From the preceding Pre-Processor data the following information can be coded.

NOTE: The following coding must start in columns as shown.

# CAGE LAYOUT CODING

## MANUAL ASSIGNMENT CODING

| 1 2 3 4  | 5 6 7 8 9 10 11 12 13 14 15 16 1 | 7 18 19 20 21 22 23 24 25 26 27 28<br>A03 | 29 30 31 32 33 34 35 36 37 3 | 8 39 40 41 42 43 44 | 45 46 47 48 49 50 51 52 |

|----------|----------------------------------|-------------------------------------------|------------------------------|---------------------|-------------------------|

| Ď        | DIZPB)                           | A03                                       | 05                           |                     |                         |

| <b>D</b> | 013PB)                           | A03                                       | 13                           |                     |                         |

| D        | 014PB'                           | A03                                       | 49                           |                     |                         |

| <u>p</u> | 0126B,                           | AO3                                       | 35                           |                     |                         |

| D        | UBR                              | R04                                       | 41                           |                     |                         |

| D        | IASM                             | B03                                       | 24                           |                     |                         |

| END      |                                  |                                           |                              |                     | /                       |

On this sample, all input/output signals were not assigned. The remainder of input/output signals were assigned by the computer.

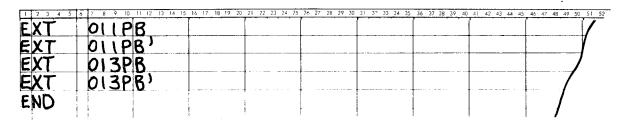

The External Signal list is used when reversal of primed and unprimed signals in the Manual Assignment list have been made. In this sample the following signals have been reversed.

## EXTERNAL SIGNALS CODING

After the above coding is complete and being processed thru the computer, the engineer may complete the schematic. However if the computer is allowed to assign the input/output signals automatically, the schematic can not be completed until the final computer print out is obtained.

# c. Schematic Completion

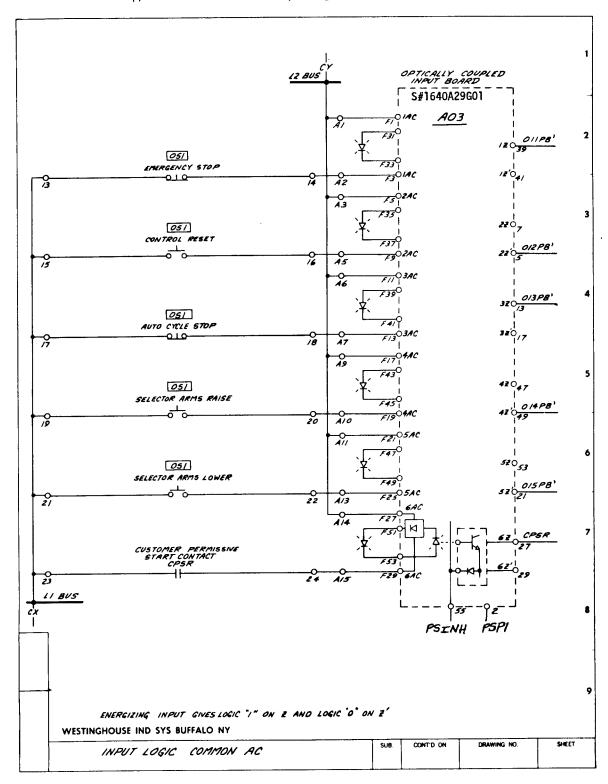

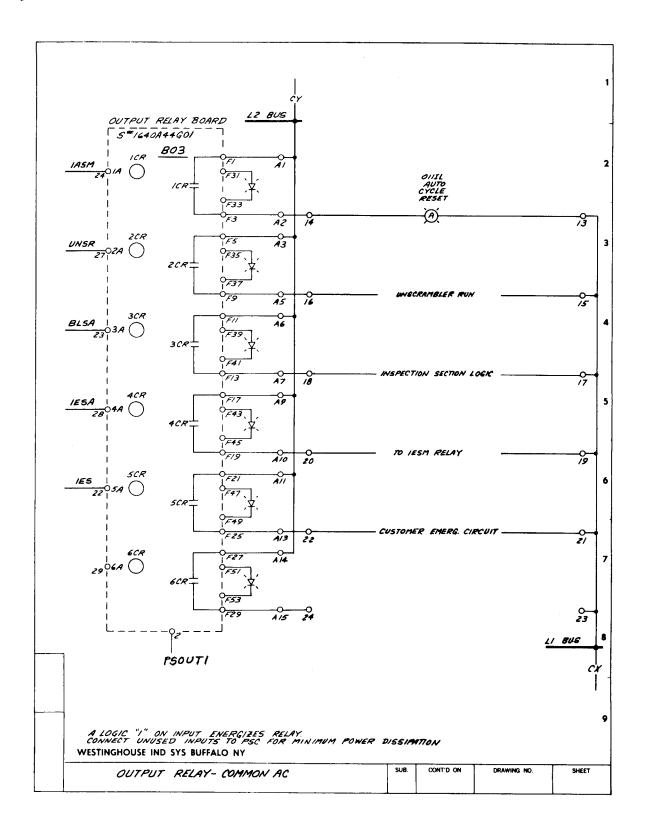

The following is only part of a OB/11 schematic. The A.C. Distribution, +5 VDC Power Supplies and 3 additional Input Eogic sheets have not been shown.

I.L.16-800-264 Page 26

This sheet of the schematic is a list of the processed logic equations, from which the required logic circuits are generated. For a schematic representation of a Logic Board see page 28.

| ELEM<br>NO  | IENT<br>Type    | INPUT<br>NO 1        | INPUT<br>NO 2          | INPUT<br>NO 3 | ОПТРИТ                     | COMPLE-                   |

|-------------|-----------------|----------------------|------------------------|---------------|----------------------------|---------------------------|

| SELEC       | TOR AR          | M AUTO LOW           | ER                     |               |                            |                           |

| 1<br>2<br>3 | N<br>N<br>N     | 1ESB<br>31T'<br>32L' | 1AS<br>ZZZ007*<br>31BA | 222008        | 318A*<br>ZZZ008<br>ZZZ007* | 31BA<br>ZZZ008*<br>ZZZ007 |

| SELEC       | IUR AR          | M AUTU RAT           | SE ON DELA             | Y             |                            |                           |

| 4<br>5      | TMR<br>N        | TTLOO1<br>MOO1ER     | TTL001                 |               | M001ER<br>31T*             | 217                       |

| 6           | N               | 1ESA                 | 1 A S                  | 31L           | TTL001 •                   | 31T<br>TTL001             |

| BILLE<br>7  | T SENS          | DR SELECTO<br>ZZZ006 | R SHORT-LOI<br>22L     | NG            | BS •                       | вѕ                        |

| 8           | N               | 222004               | 222005                 |               | 222006                     | 222006                    |

| 9<br>10     | N<br>N          | 013S2<br>013S1       | 23L<br>21L             |               | ZZZ005 •<br>ZZZ004 •       | 222005<br>222004          |

| SELEÇ<br>11 | TOR STO         | OPS SIZE L           | ARGE SOLEN             | DID RAISE     | 21 BR *                    |                           |

|             | 1014            |                      |                        |               | 2100                       |                           |

| 12<br>SELEC | N<br>TOR STO    |                      | BS!<br>MALL SOLENO     | 21AR *        | 21BR*                      | 21BR                      |

| 13          | TRIA            | 5, 5 512C 5,         | TALE SOLEN             | DID COMEN     | 21 AR •                    |                           |

| 14<br>SQUAR | N<br>ING ST     | 01281<br>OP LOWER SO | BS'<br>OLENOID         | 21BR *        | 21 AR *                    | 21AR                      |

| 1.5         | TOTA            |                      |                        |               | 11001                      |                           |

| 15<br>16    | TRIA<br>N       | 01152                | 11AR*                  |               | 11BR*<br>11BR*             | 118R                      |

|             |                 | OP RAISE SO          |                        |               |                            |                           |

| 17<br>18    | TRIA<br>N       | 01151                | 11BR*                  |               | 11AR*<br>11AR*             | 11AR                      |

|             |                 |                      |                        |               |                            | LLAN                      |

| UNSCR<br>19 | AMBLER<br>CLAR  | PERMISSIVE           | E                      |               | UNSR                       |                           |

| 20          | N               | 8 S *                | 32L                    | 1ESA          | UNSR*                      | UNSR                      |

| AUTO<br>21  | S E QUENC       | E MASTER S<br>02151  | SWITCH<br>1ASM         | 1ESA          | 1AS*                       | 145                       |

|             |                 |                      | 1830                   | IEJA          | 143                        | IAS                       |

| AUTO<br>22  | SEQUENO<br>N    | CE RESET             | 1ASM                   | 1ESA          | 1ASX'                      | 1 ASX                     |

| 23          | N               | 015PB                | 1ASX*                  | 1234          | 222003                     | 222003                    |

| AUTO<br>24  | SEQUENO<br>CLAR | CER MASTER           |                        |               | 1ASM                       |                           |

|             | •               | 0.1.2.2.2.4          |                        |               |                            |                           |

| 25<br>26    | N<br>N          | 013PB • 014PB •      | ZZZ002<br>1ASM!        | 1ESA          | 1ASM'<br>ZZZ002            | 1 A S M<br>Z Z Z O O 2 *  |

|             | SELECTO         |                      |                        |               |                            |                           |

| 27<br>28    | CLAR<br>N       | BLS                  |                        |               | BLSA<br>BLSA               | BLSA                      |

| 29          | N               | 0165                 |                        |               | BLS.                       | BLS                       |

| EMERG       | ENCY MA         |                      |                        |               | 1E\$B*                     | 1ESB                      |

| 30<br>31    | N<br>CLAR       | 1ES                  |                        |               | 1ESA                       | 1630                      |

| 32          | N               | 1ES                  |                        |               | 1ESA*                      | 1 E S A                   |

| 33          | CLAR            |                      |                        |               | 1ES                        |                           |

| 34          | N               | CPSR                 | 011PB*                 | 222001        | 1ES*                       | 1ES                       |

| 35          | N               | 012PB •              | 1ES*                   |               | 222001                     | 222001                    |

| DRAWING | SUB | SHEET | SHEETS |

|---------|-----|-------|--------|

|         |     | NO.   |        |

This sheet of the schematic is a list of input equations. These are the exact equations written by the designer.

```

OUTR 1ES = CPSR * 011PB* * (012PB + 1ES)

OUTR

1ESA= 1ES

1ESB= 1ES

EMERGENCY MASTER

BLS = 016S

OUTR

BLSA= BLS

LINE SELECTOR

С

OUTR 1ASM= 013PB* * (014PB + 1ASM) * 1ESA

AUTO SEQUENCER MASTER

C.

1ASX= (015PB + 1ASX) * 1ASM * 1ESA

AUTO SEQUENCE RESET

1AS = 021S1 * 1ASM * 1ESA

AUTO SEQUENCE MASTER SWITCH

OUTR

UNSR= BS* * 32L * 1ESA

UNSCRAMBLER PERMISSIVE

OUTT

11AR= 011S1 * 11BR*

SQUARING STOP RAISE SOLENOID

OUTT

11BR= 011S2 * 11AR*

SQUARING STOP LOWER SOLENOID

21AR= 012S1 * BS* * 21BR*

OUTT

SELECTOR STOPS SIZE SMALL SOLENOID LOWER

21BR= 012S2 * BS* * 21AR*

OUTT

SELECTOR STOPS SIZE LARGE SOLENOID RAISE

BS = ((013S1 * 21L) + (013S2 * 23L)) * 22L

BILLET SENSOR SELECTOR SHORT-LONG

TM005 31T = 1ESA * 1AS * 31L

SELECTOR ARM AUTO RAISE ON DELAY

31BA= 1ESB * 1AS*(31T + (32L** 31BA))

SELECTOR ARM AUTO LOWER

END

```

| DRAWING | SUB | SHEET | SHEETS |

|---------|-----|-------|--------|

|         |     | NO.   |        |

|         |     |       |        |

This sheet of the schematic is a list of the back panel wiring (Sorted Signal List).

### SORTED SIGNAL LIST

| SIGNAL | NAME | CON- | PIN | C   | N-PI | N |   | CON- | ИІЧ |   | CON- | PIN |     | CON-PI | N C | ON-PI        | N COI          | N-PI |

|--------|------|------|-----|-----|------|---|---|------|-----|---|------|-----|-----|--------|-----|--------------|----------------|------|

| BLS    | 8 5  | 18   | 8   | 5 4 | 7    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| BLSA   | В 3  |      | В   | 5 4 | 9    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| 8 S *  | 8 6  | 6    | В   | 6 4 | 0    | В | 6 | 16   | В   | 6 | 19   |     |     |        |     |              |                |      |

| CPSR   | A 3  | 27   | В   | 5   | 6    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| MOOLER | A 7  | 10   | 8   | 7   | 6    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSINH  | A 1  | . 6  |     |     |      | A |   | 55   | A   | 5 | 55   | A   | 6   | 55     |     |              |                |      |

| PSOUT1 | A 1  | 29   | В   | 3   | 2    | В | 4 | 2    |     |   |      |     |     |        |     |              |                |      |

| PSP1A  | A 1  | 33   | В   | 1   | 3    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP1B  | A 1  | 4    | В   | 1 3 | 32   |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP1C  | A 1  | 34   | В   | 1 3 | 3.   |   |   |      |     |   | •    |     |     |        |     |              |                |      |

| PSP1   | A 1  | . 3  | A   | 3   | 2    | A | 4 | 2    | A   | 5 | 2    | A   | 6   | 2      |     |              |                |      |

| PSP2A  | A 1  | 57   | В   | 1   | 6    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP2B  | A 1  | . 28 | 8   | 1   | 35   |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP2C  | A 1  | . 58 | В   | 1   | 36   |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP3A  | A 1  | 48   | 8   | 1   | 39   |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP3   | A 1  | 18   | В   | 1   | 9    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP4A  | A 1  | . 56 | В   | 1 4 | 1    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| PSP4   | A 7  | 2    | Α   | 7   | •    |   |   |      |     |   |      |     |     |        |     |              |                |      |

| TTL001 | A 7  | 39   | ^   |     |      |   |   |      |     |   |      |     |     |        |     |              |                |      |

| UNSR   | В 3  | 3 2- |     |     |      |   |   |      |     |   |      |     |     |        |     |              |                |      |

| 222001 | D    |      |     |     |      |   |   |      |     |   |      |     |     |        |     |              |                |      |

| 222002 |      |      |     |     |      |   |   |      |     |   |      |     |     |        |     | <del>,</del> | <del>, ,</del> |      |

| 7'     |      |      |     |     |      |   |   |      |     |   |      | DF  | RAW | ING    | SUB | SHEET        | SHEETS         |      |

| -      |      |      |     |     |      |   |   |      |     |   | - 1  |     |     |        |     | NO           |                |      |