#### GATE PULSE GENERATOR

# INTRODUCTION

A general purpose gating system which utilizes a linear ramp for phase control and which can provide phase control ranges of 1500, 1800 or 2100 is comprised of the Thyristor Gate Driver S#1668A25, the Gate Pulse Generator S#1671A17 and the Gate Synchronizer S#1684A02 (S#1684A05 for 50 hz).

The Gate Pulse Generator (GPG S#1671A17) generates three output pulse trains spaced at  $120^{\circ}$  intervals for use in a three thyristor power module. A second duplicate GPG is required in a six thyristor power module to provide a total of six output pulse trains spaced at  $60^{\circ}$  intervals.

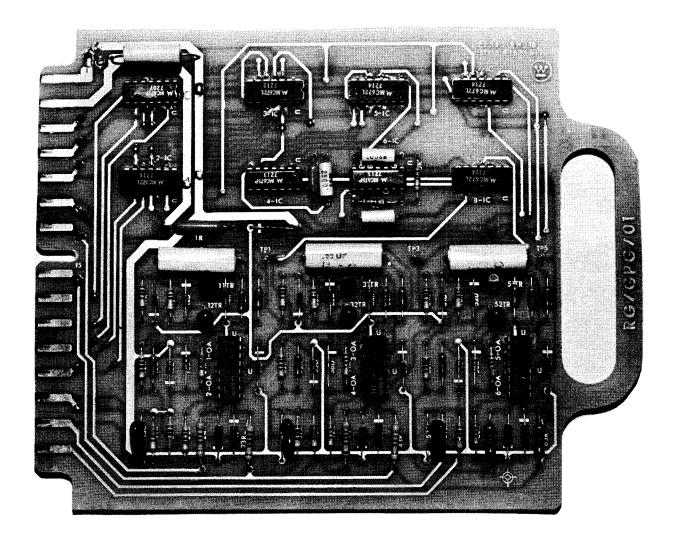

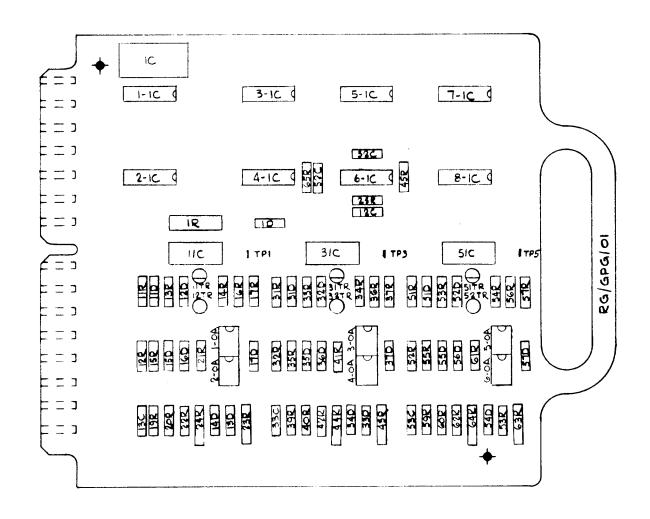

Figure 1 is a picture of the GPG. A front view locating all components by schematic identification is shown on the last page of the instruction leaflet.

FIGURE 2

# II. DESCRIPTION OF OPERATION

#### A. INTRODUCTION

The Gate Pulse Generator (GPG) is a system which generates gate pulses for power thyristors at the gating angle determined by an input control voltage. The conversion from the input control voltage to the output gating angle is done by the use of a locally generated linear timing ramp. The timing ramp is synchronized to the power thyristor's commutation voltage by an externally supplied synchronizing signal.

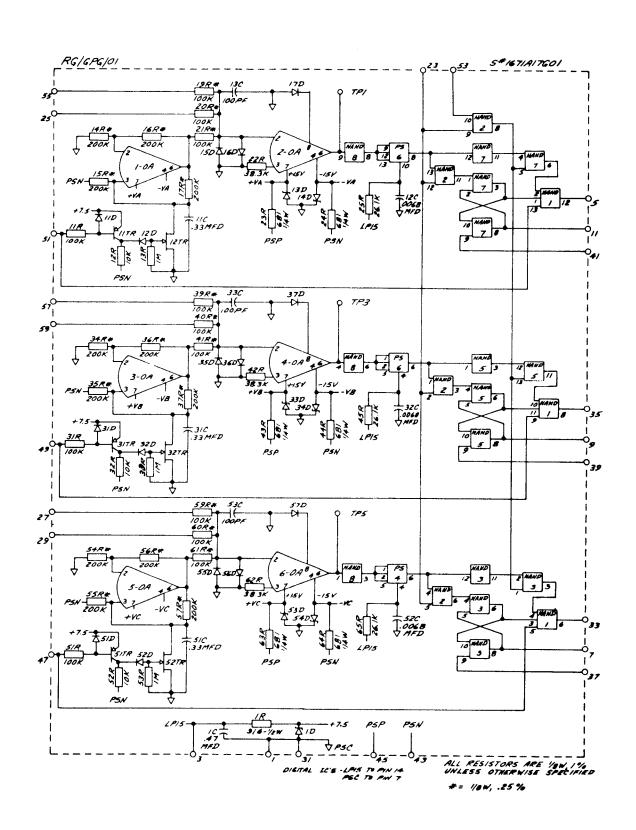

Each GPG pc board has three identical generator circuits providing for picket fence pulse trains spaced at 1200 intervals. For a six pulse system an additional GPG pc board is used. A complete gating system requires a synchronizing function and an amplifier which drives the power thyristor with the picket fence pulse train.

## B. DESCRIPTION

#### 1. Gate Pulse Generation

For purposes of illustration a functionalized circuit diagram is provided by Figure 3.

### a. Synch.

SYNCH is a digital input signal which is in synchronism with the commutation voltage of the power thyristor whose gating angle is to be controlled. When SYNCH is a logic 1, the static relay (a Field Effect Transistor) is open allowing the capacitor C to be charged by the constant current source I

## b. Timing Ramp

The voltage on the capacitor is a highly linear negative going ramp from which the gating angle can be determined. The ramp is fed into voltage comparator VC along with the control voltage V(C). The point on the ramp at which the comparator switches from a logic 0 to a logic 1 is controlled by V(C). The comparator is reset when SYNCH goes to a logic 0, which closes the static relay discharging capacitor C.

# c. 50 µSec Hard Pulse

The logic 1 of the comparator is "shrunk" by the pulse shrinker PS to a pulse 50  $\mu$ Sec long. This pulse serves as the hard first pulse of the picket fence pulse train as well as to set flip-flop 1-FF. The hard pulse is OR'ed with an externally supplied oscillator signal and then this signal is NAND'ed with the Q output of flip-flop 1-FF to form the picket fence pulse train.

The purpose of the 50  $\mu$ Sec hard first pulse is to assure that the initial pulse applied to the power thyristor gate is adequate to gate the device completely ON for any load conditions. The oscillator signal, which contributes the remainder of the pulse train, is not synchronized with the gating angle or any other signal. Therefore, its phase and frequency relationship to the hard pulse is impossible to predict.

# d. Ring Counter

Flip-flop's 1-FF, 2-FF and 3-FF are tied together in a ring counter. A flip-flop is turned ON (Q = 1) by its respective set signal (the 50  $\mu$ Sec pulse) and is turned OFF by the turning ON of the succeeding flip-flop. Consequently, the only one of the three channels that may generate a picket fence pulse train at any one time is the one in which the most recent 50  $\mu$ Sec pulse has occurred.

## e. Tail end Chop

A third input is provided on the output NAND to prevent the picket fence pulse train from continuing past a critical gating angle regardless whether or not the flip flop has been reset. The action is performed by the negative transition of the SYNCH signals; i.e. when SYNCH = 0 the picket fence pulse train is chopped OFF, hence tail end chop. This feature prevents the power thyristor from being gated for an extended time while it is reverse biased.

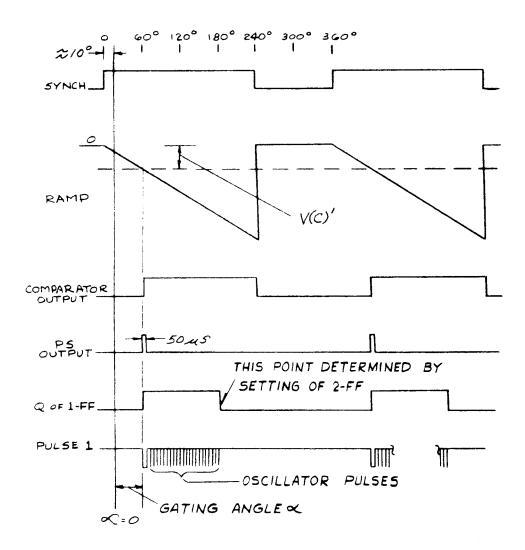

Waveforms for a symmetrical three pulse system are shown in Figure 6.

FIGURE 6

Advance and retardation limits on the gating angle  $\alpha$  are fixed by voltage limits on V(C)'. The range of control for this system is sufficient for 0 to 210 degrees at 60 or 50 Hz. Note that the SYNCH signal releases the ramp approximately 10 degrees before  $\alpha$  = 0. This prevents advance limit from occurring at the starting point of the ramp.

# III. CHARACTERISTICS AND RATINGS

|    |                                                                                                                                |                                          | MIN                        | MAX              | UNITS          |

|----|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|------------------|----------------|

| Α. | LOGIC DEFINITIONS                                                                                                              |                                          |                            |                  |                |

|    | Logic 1<br>Logic 0                                                                                                             |                                          | +12.5<br>0                 | +15.0<br>+1.5    | Volts<br>Volts |

| В. | INPUTS                                                                                                                         |                                          |                            |                  |                |

|    | <ol> <li>Control Voltage V(C)ranginput impedance/char</li> </ol>                                                               |                                          | Preset by Gate Synchronzer |                  |                |

|    |                                                                                                                                |                                          | -10°                       | -10 <sup>0</sup> | K Olimo        |

|    | 2. SYNCH switch to logic 1 switch to logic (                                                                                   |                                          | 230 <sup>0</sup>           | 230 <sup>0</sup> |                |

|    | frequency                                                                                                                      | , ac a -                                 | 45                         | 65               | Hz             |

|    | digital load fact                                                                                                              | tor/channel                              |                            | 1                |                |

|    | 3. GPS Logic 0 = Suppressi                                                                                                     | on of gate pulses<br>load factor (total) |                            | 4                |                |

|    | 4. OSC Waveform                                                                                                                |                                          |                            |                  |                |

|    | digital load factor (total)                                                                                                    |                                          |                            | 1                |                |

| С. | , ОИТРИТ                                                                                                                       |                                          |                            |                  |                |

|    | 1. Pulse 1, 2 and 3 Wavefor                                                                                                    | orm                                      |                            |                  |                |

|    | digital load factor/channel mismatch between channels at max $\alpha$                                                          |                                          | 8<br>4°                    |                  |                |

|    | <ol> <li>Ring Counter terminations (pins 11, 41, 9, 39,</li> <li>7 &amp; 37) use for interconnection purposes only.</li> </ol> |                                          |                            |                  |                |

| D. | GAIN (over temperature range)                                                                                                  |                                          |                            |                  |                |

|    | 1. Group 1: at 60 Hz α/\                                                                                                       | ν(c) <sup>'</sup>                        | .51                        | .53              | Rad/Volt       |

|    | at 50 Hz α/V                                                                                                                   | (c) <sup>'</sup>                         | .42                        | .44              | Rad/Volt       |

| Ε. | POWER SUPPLY REQUIREMENTS                                                                                                      |                                          |                            |                  |                |

|    | PSP (pin 45)                                                                                                                   | Volts<br>Current                         | +23                        | +25<br>50        | Volts<br>mA    |

|    | PSN (pin 43)                                                                                                                   | Volts<br>Current                         | -23.99                     | -24.01<br>60     | Volts<br>mA    |

|    | LP15 (pin 3)                                                                                                                   | Volts<br>Current                         | +13.5                      | +16.5<br>70      | Volts<br>mA    |

| F. | OPERATING TEMPERATURE                                                                                                          |                                          | 0                          | +55              | o <sub>C</sub> |

FIGURE 7