# THREE PHASE UNINTERRUPTIBLE POWER SUPPLIES

**CUSTOM POWER EQUIPMENT DEPARTMENT**

PHILADELPHIA, PA.

#### TABLE OF CONTENTS

| SECTION 1: OVERALL SYSTEM                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

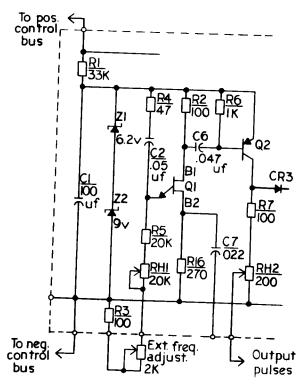

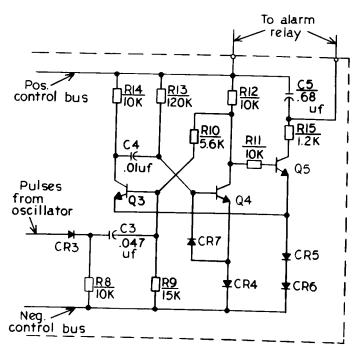

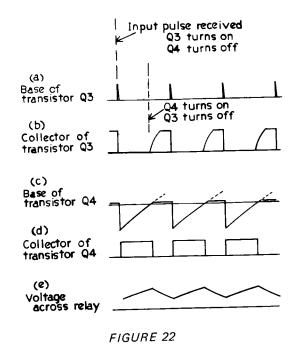

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRODUCTION RECEIVING & HANDLING SYSTEM DESCRIPTION NON-REDUNDANT REDUNDANT WITH BY-PASS SWITCHGEAR UPS MAJOR COMPONENTS BATTERY CHARGER INVERTER MASTER CONTROL BATTERY TURN-ON PROCEDURE TURN-OFF PROCEDURE MONITORING OF VOLTAGES MAINTENANCE                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SECTION 2: BATTERY CHARGER                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GENERAL INFORMATION DESCRIPTION OF COMPONENTS OPERATION TURN-ON PROCEDURE OVERVOLTAGE ADJUSTMENT COOLING SYSTEM SECTION 3: INVERTER                                                                                                                                                                                                                                                   | 8<br>9<br>9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GENERAL INFORMATION COMMUTATION VOLTAGE CONTROL INVERTER HALF-BRIDGES DELAYED GATING SYNCHRONIZATION PHASE SHIFT CONTROL POLYPHASE INVERTERS POLYPHASE INVERTER CONTROL CONTROL FOR SIX PHASE INVERTER CONTROL FOR TWELVE PHASE INVERTER                                                                                                                                              | 11<br>12<br>13<br>13<br>13<br>13<br>14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SECTION 4: INVERTER AUXILIARY CIRCUITS                                                                                                                                                                                                                                                                                                                                                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GENERAL INFORMATION DETAILED INVERTER STARTING SEQUENCE                                                                                                                                                                                                                                                                                                                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SECTION 5: MASTER CONTROL                                                                                                                                                                                                                                                                                                                                                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

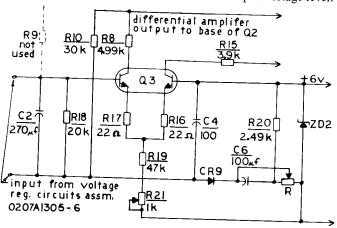

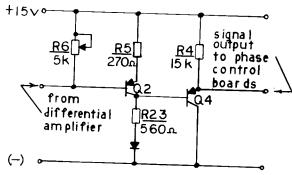

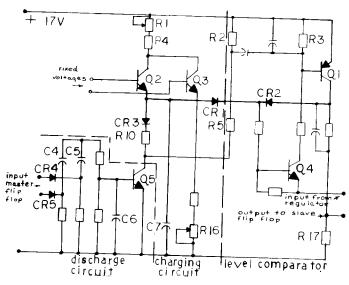

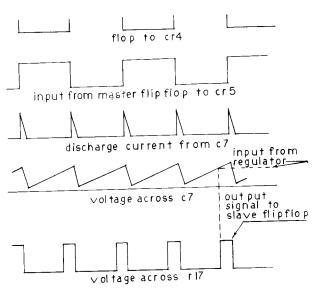

| GENERAL INFORMATION MASTER OSCILLATOR OPERATION FIELD ADJUSTMENTS MONOSTABLE ASSEMBLY MULTIVIBRATOR DIFFERENTIATOR VOLTAGE REGULATOR AUXILIARY REGULATOR CKT. CENTRAL VOLT. REGULATOR PHASE CONTROL CKT. CHARGING CKT. DISCHARGING CKT. LEVEL COMPARATOR MASTER FLIP-FLOP SLAVE FLIP-FLOP SCR PULSE AMPLIFIER 17 VOLT POWER SUPPLY 48 VOLT POWER SUPPLY SECTION 6: IMPEDANCE INSERTER | $\begin{array}{c} \dots 17 \\ \dots 17 \\ \dots 20 \\ \dots 20 \\ \dots 21 \\ \dots 21 \\ \dots 21 \\ \dots 22 \\ \dots 22 \\ \dots 23 \\ \dots 23 \\ \dots 23 \\ \dots 24 \\ \dots 25 \\ \dots $ |

| GENERAL INFORMATION PRINTED CKT. BOARD DESCRIPTION PCB-0207A5311 & PCB-0207A5312 PCB-0207A5313 & PCB-0207A5314  DETAILS OF OPERATION SWITCHING POWER ON OVERCURRENT TRIP TRIP SIGNAL FROM FUSE MONITOR D.C. UNDERVOLTAGE TRIP A.C. UNDERVOLTAGE TRIP MANUAL TURN OFF                                                                                                                  | 27<br>27<br>28<br>29<br>30<br>31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

H1897

#### **SECTION I: OVERALL SYSTEM**

#### INTRODUCTION

The advent of computer technology and its widespread application to commercial and industrial enterprises has created a need for a power source which is entirely free from voltage dips and interruptions, even of the order of a few cycles. Computers are not alone in this respect. Other critical loads include vital communication links, power distribution telemetry, and the like.

Commercial power distribution systems cannot satisfactorily supply service to these critical loads because of the nature of distribution practices. Lightning strokes, tree contact, and rodent damage are examples of events which can cause interruption of electrical power. These interruptions can be frequent, and can adversely affect critical loads even if their duration is a matter of seconds or even cycles.

Various types of apparatus have been devised to isolate the critical load from disturbances on the distribution sys-These include M-G sets with flywheels, clutches, diesels, etc. in various configurations. None of these performs as well as General Electric's Uninterruptible Power Supply system. This system with its solid state components features fast response (order of microseconds), quiet operation, stable output frequency regardless of loading, no special foundations or shaft alignment, and long life with minimum maintenance. The rectifier and inverter technology on which these systems are based is not new and has been treated in other publications. However, the combined application of these equipments complete with control and storage battery calls for instructional information which embraces the entire system. It is the purpose of this book to present a detailed description of the Uninterruptible Power Supply, the various types, function of major components, and operation of subassemblies and circuits. It is intended as an aid to the user in getting optimum performance from his equipment. It is also intended that the elementary diagram supplied with the equipment be used as a companion to this manual, since the elementary diagram contains a schematic of all the circuits described.

#### **RECEIVING & INSTALLATION**

Installation consists of unpacking, setting up the apparatus and making connections between the various assemblies. A few suggestions are given here, however, the actual methods used are dependent upon the local conditions existing at the time of installation.

This equipment is assembled, tested, and packed with care to enable the purchaser to install and place it in operation with a minimum of time and labor. Immediately upon receiving the equipment, it should be carefully checked against the memorandum of shipment. If any parts are found damaged, or missing, the purchaser should immediately present a claim to the Transportation Company and notify the nearest sales office of the General Electric Company.

It is good practice to place the equipment as near as possible to its permanent location before unpacking. The standard type of unpacking tools should be used. A nail puller can be especially useful. Careless unpacking methods will invariably result in parts being damaged or marred. Some parts such as bolts and screws are packed in special containers to keep them together; however, they may become separated. Therefore, packing material should not be discarded until it is certain that all parts have been removed. Equipment should be thoroughly cleaned to remove particles of packing materials or foreign substances which may have become lodged in or between any of the parts. Apparatus not immediately installed should be labeled and set aside in a clean dry place of moderate temperature and protected from injury.

When equipments are installed, ample space should be provided around the various parts to permit easy inspection, adjustment, and repair. Whenever possible all control devices are mounted at the factory; interconnections are made and leads are brought out to numbered terminals, making it necessary only to install the component pieces and connect the numbered terminals to the various pieces of apparatus. The remote interconnection diagrams supplied should be used as a guide for making the connections.

When the equipment has been set up, it should be thoroughly inspected and checked to be sure that all connections are complete and tight, that the relays and instruments are in good mechanical condition, that they have been thoroughly cleaned, and that all of the movable parts work freely. All devices should make good contact and have clean contact surfaces.

#### SYSTEM DESCRIPTION

#### **NON-REDUNDANT UPS**

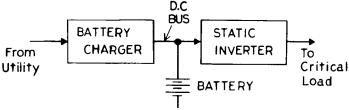

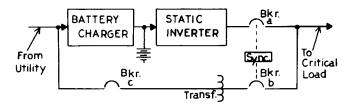

The simplest form of uninterruptible power supply (UPS) utilizes a regulated rectifier, an electrical storage battery, and a static inverter. A single line diagram of this kind of system is shown in Figure 1.

During normal operation the battery charger converts the incoming AC to a regulated DC bus voltage. The DC bus then supplies the power to the static inverter which converts it to AC power with the characteristics described below. Since the AC output is produced from DC power by the static inverter, the control system of the static inverter alone governs the characteristics of the AC output.

Any fluctuations in voltage or frequency which occur on the power distribution system are completely isolated from the critical load.

FIGURE 1 SINGLE LINE DIAGRAM OF NON-REDUNDANT UPS

In the event of either a momentary or prolonged failure of the owner's normal source of commercial power, the electrical storage battery will furnish the DC power needed to operate the static inverter. The battery is continually connected to the DC bus so that it is always available to supply electrical energy whenever it is required. This arrangement is defined as a "Floated Battery" system, because the battery is constantly available without the need of any switching operation. (Since a battery charger can transmit electrical power in one direction only, the battery cannot feed power back into the commercial power system. Thus, there is no danger of discharging the battery into a dead commercial power system.)

Once the normal power to the UPS has been restored, the regulated rectifier will resume supplying the inverter, and at the same time the regulated rectifier will recharge the battery.

#### **REDUNDANT UPS**

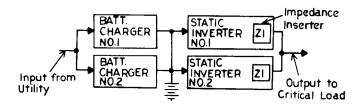

The simplest UPS described above suffers from one very serious flaw. A failure of the static inverter interrupts power to the critical load. Thus, the reliability of the UPS cannot be made any greater than the reliability of the inverter itself. While solid state inverters are a very reliable class of equipment, they are not perfect; so that an eventual inverter failure must be expected. However, by using a "Redundant" System it is possible to overcome this limitation and to provide a UPS which has an overall system reliability that is actually greater than the reliability of any individual component of the UPS.

FIGURE 2 - SINGLE LINE DIAGRAM OF REDUNDANT UPS

The obvious way to avoid the complete dependence on a simple static inverter is to provide two such inverters connected in parallel. Unless special precautions are taken, however, a failure in either of the two inverters will cause the voltage of the critical bus to collapse. Thus a failure in either inverter will fail the entire UPS. Clearly the overall reliability of this arrangement is no better than before. In fact, it is worse, since there is almost twice the chance for a failure to occur in either of the two inverters as there is for a failure to happen in only one inverter. Thus, if redundant inverters are going to be used, a means must be devised to prevent a failure in any one inverter from affecting the overall system performance. This means that any inverter which fails must be removed from the system immediately, well before the effects of failure are felt at the critical bus. A solid state "Impedance Inserter" has been provided between each inverter and the critical bus to accomplish this function. Whenever a fault is sensed within one of the redundant inverters, the appropriate impedance inserter immediately isolates the offending inverter from the system. (See Section 6 for detailed ZI functions.) Tests have shown this isolation is accomplished before the system output is disturbed. A simplified diagram of a redundant UPS with impedance inserter is shown in Figure 2. Also note that two battery chargers have also been provided in case one charger should fail.

Except for either a failure within the UPS or a fault within the critical load; the operation of the redundant UPS is the same as the operation of the simple non-redundant UPS. The only differences are as follows:

- 1. Whenever an internal failure develops within one of the redundant inverters, this failure is sensed by the impedance inserter and the offending inverter is immediately disconnected from the system.

- 2. If the system becomes overloaded or if a short circuit develops in the critical load, the UPS is called upon to deliver greater current than it is capable. Under these circumstances this impedance inserter will limit the load current by introducing a high impedance into the feeders leading to the critical bus. If this excessive current is not reduced to normal within three seconds, the ZI takes the inverter off the line by tripping the inverter output breaker.

#### **UPS WITH BYPASS SWITCHGEAR**

A complement of circuit breakers, complete with the necessary transformer and synchronizing equipment, can be added to the UPS. A single line diagram of a simple by-pass system is shown in Figure 3. This by-pass switchgear is used to feed the critical load from the utility source while the UPS is off the line for maintenance or inspection. The synchronizing equipment enables an operator to place the

inverter output in phase with the commercial power source, allowing Breaker (b) to be closed, which sets up a momentary paralleling situation. Breaker (a) can then be opened, fully transferring the load to the utility. Power flow to the critical load is not interrupted during this transfer.

FIGURE 3 - SINGLE LINE DIAGRAM OF UPS WITH BY-PASS SWITCHGEAR

An automatic transfer to the by-pass switchgear can also be achieved. In this type arrangement, the inverter output is kept in phase-lock with the utility source through a special phase discriminator circuit. Transfer to by-pass can, of course, be accomplished manually. If, however, the inverter should fail or load conditions are such that failure is imminent, a transfer to by-pass will be automatically initiated. Except for the very rare case where the inverter has a total internal failure, the transfer to by-pass is a make-before-break transition so there is no interruption of power to the load.

An additional refinement in the form of a static bypass can also be incorporated into a UPS. It is essentially an "instantaneous close" circuit breaker applied in parallel with the conventional by-pass circuit breaker. In this arrangement, the inverter output is again kept in phase-lock with the utility source. Even in the case of a total internal failure in the inverter, the static by-pass (instantaneous close circuit breaker) is electronically switched on at the same time as the impedance inserter in the inverter. Thus power flow to the load is never interrupted. A few cycles after the static switch is closed, the conventional by-pass circuit breaker closes it's contacts, shorts out the static breaker, and carries current to the load.

#### **UPS MAJOR COMPONENTS**

This section describes the equipments which make up the UPS system, i.e. Battery Charger, Inverter, Master Control, and Station Battery. It also describes the major circuits associated with each equipment and the function performed.

#### **BATTERY CHARGER**

Input power comes from a three pole, manually-operated circuit breaker to the primary of the three-phase transformer. The purpose of the transformer is to change the a-c primary voltage to the level required to obtain the desired output of

405 Volts d-c at maximum conduction angle. A three-phase control-power disconnect is provided to isolate the control circuits in the unit.

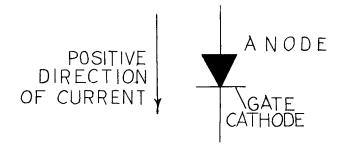

The rectification of the a-c voltage is accomplished by the SCR (thyristor) power modules. The basic power module consists of a three phase bridge circuit, with each leg of the bridge containing SCR cells and a series current limiting fuse. An SCR is a phase controlled rectifying device which is controlled by applying a signal to the gate lead during the positive half cycle of the a-c voltage wave (anode of SCR positive with respect to cathode), causing the SCR to conduct as an ordinary rectifier. When the applied a-c voltage reverses in polarity, the SCR will turn off until the next gate signal is applied. A neon light is shunted across each SCR to indicate failure of SCR or fuse. Gate signals to fire the SCR's are produced by a gate pulse generator which is, in turn, controlled by the regulating amplifier module. Details of the gate pulse generator are contained in a separate instruction book, GEI-90837. Details of the regulating amplifier are contained in GEK-13522.

A filter is placed in the output to limit ripple voltage. The silcomatic rectifier is protected against normal voltage transients, such as produced by switching and other line disturbances, by surge suppressors connected to both the a-c and d-c buses.

The output voltage of the battery charger is regulated by continuous adjustment of the time in the power cycle at which the SCR's are gated. The regulating circuit is of an internal closed-loop type. A feedback signal proportional to the d-c output voltage is compared to a reference signal and the resultant error is fed to the control circuit. This signal will cause a shift in the gating pulse of the thyristors; resulting in their firing at different times in the power cycle.

A current walk-in feature is provided to prevent excessive current when the input circuit breaker is closed and the silcomatic rectifier is connected to a load, such as a battery or filter capacitors on the d-c bus.

To protect against battery overcharge after an outage, current-limit is integrated into the regulating circuit. The current-limit utilizes an inverse voltage-current relationship to control the battery charger output. Should the current exceed this relationship at a given d-c voltage, the regulator circuit will cause the SCR's to fire at a later time on the power cycle and reduce the output voltage. The voltage will drop until the inverse current-voltage relationship is met. If the d-c voltage exceeds the maximum rated, the overvoltage relay will open the incoming a-c breaker and shut down the regulated rectifier.

A thermotector is embedded in the input transformer to protect the transformer from overheating. When the transformer temperature reaches the thermal design limit, the input breaker is tripped. Fan failure on any of the rectifier cubicles trips the input breaker.

See Section 2 - Battery Charger for more detailed information.

#### INVERTER

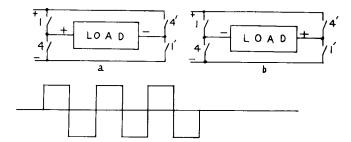

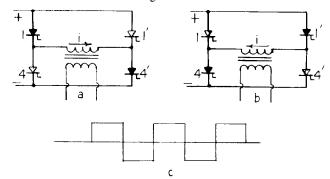

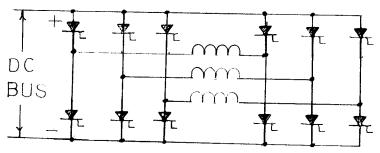

The static inverter is used to convert d-c voltage to stepped sine-wave voltage. It utilizes phase-controlled SCR's in a bridge-type circuit to chop the d-c voltage into pulses, which are combined and filtered to approximate a sine-wave voltage. The inverter input operating range is 320 to 405 VDC.

A starting circuit is used to initially charge the d-c filter capacitors, which will, when charged, pick up the d-c voltage relay. This voltage relay initiates a sequence of events which removes the starting circuit from the power circuit. The a-c output breaker can not be closed until this sequence is completed.

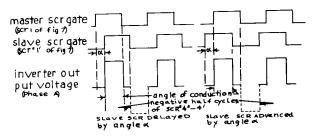

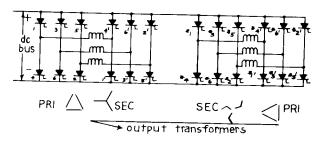

The d-c power is fed in the output transformer through the inverter SCR cells. Each primary winding of the output transformer is connected between the positive and negaative d-c buses but is electrically isolated from each bus by a set of forward and reverse SCR cells. Firing the forward set of cells allows a positive rectangular pulse of d-c voltage to be applied to the winding. The voltage magnitude of this pulse is equal to the value of the d-c bus voltage. The duration is controlled by the overlap in the conducting period of the positive d-c bus thyristor with respect to the negative d-c bus SCR. No voltage appears across the transformer primary winding until both the cells are gated on. The turnon of the negative bus cell can be delayed with respect to the turn-on of the positive bus cell, hence, the width of the voltage square-wave (or average voltage) impressed on the primary winding can be controlled. The inverter employs six such pairs of thyristors and three transformer primary windings.

Proper gating of the cells results in a stepped voltage wave being impressed on the primary of the transformer. The secondary windings are connected in a zig-zag configuration to decrease output harmonic content. This output is then filtered to attenuate remaining harmonics.

Output frequency is controlled by the frequency at which the SCR power cells are gated. The gating circuit is triggered by a solid-state fixed frequency (adjustable + 1 CPS), oscillator and generates a voltage pulse which is amplified to gate the inverter thyristors. Since the oscillator is electrically independent of the power circuit, the output frequency is unaffected by system loading. Voltage control changes only the phase relationship of the gating signals without affecting their frequency.

The voltage regulation system is of the closed loop type. A feedback signal, proportional to the average of the output phase voltages, is compared to a reference signal and the re-

sultant error is fed to the control circuit. This causes an advance or delay in the gating pulses of certain cells which will result in a relative shift in the firing time of the negative bus SCR with respect to the positive-bus cell. This shift in the gating time will change the duration of voltage pulse across the output voltage. The level of the output voltage is changed by adjusting the reference signal potentiometer.

In a redundant system, a static interrupter is placed in series with the output breaker of each inverter to prevent excessive critical a-c bus transients in the event of an internal fault in an inverter. It consists of a set of back-to-back SCR's, shunted by an impedance, in each of the three phases. During normal operation, the SCR's are continuously energized so that they pass alternating current with only the forward drop of the cell in series with the output voltage.

In the event of a critical bus fault, a pre-charged capacitor back biases the cells which were conducting and causes them to block, thus inserting impedance into the circuit to limit current from the inverter system. The inverter system will operate in the current limit mode for a preset interval (approximately 3 seconds) after which the system output breaker will trip. Downstream protective devices should be selected to clear within the 3 second interval to assure load-fault protection. Current available in the current limit mode is the sum of full load currents from each inverter in the system. If an internal inverter fault occurs, the static interrupter disconnects the faulted inverter from the critical bus. This is done quickly enough to prevent the other inverters from seeing the fault. See Section 3 & 4 - Inverter and Section 6 - Impedance Inserter for more detailed information.

#### **MASTER CONTROL**

The Master Control compartment(s) is part of every UPS. It houses the electronic control for the system and also some instrumentation. Electronic power supplies to provide excitation for the control circuits are also included in the master control. Voltage relays and synchronizing devices (when required) are also mounted here. These synchronizing devices are associated with transfer to the by-pass switchgear when it is present and are located on a front door for accessibility. The electronic control for the system utilizes solid state components mounted on printed circuit boards to perform various functions, including:

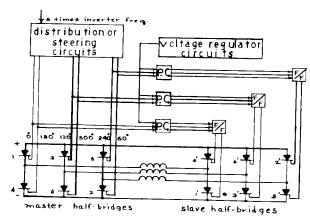

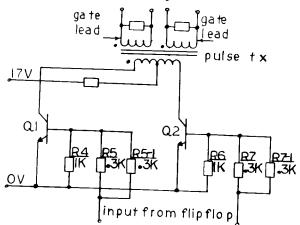

- Oscillators to establish and control the UPS output frequency by generating the basic pulses ultimately used to gate the inverter SCR's.

- 2) The monostable circuit to combine the output of the oscillators and form a single train of pulses\*.

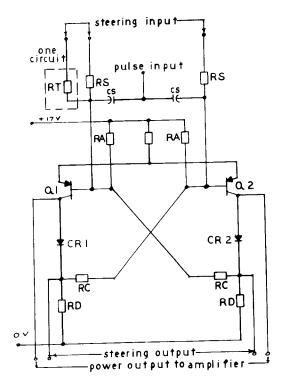

- 3) The master flip-flop circuits which take the train of pulses from the monostable circuit and act in conjunction with a steering signal to produce gate pulses

- for the SCR's in the master inverter carts. The steering circuits assure that the flip-flops operate as required to obtain the correct positive and negative a-c half cycles and also the correct phase sequence at the inverter output.

- 4) Slave flip-flop circuits which are actuated by the master flip flops and produce gate pulses for the SCR's in the slave inverter carts. The output of the slave flip-flop can be delayed by the action of the phase control boards. This, in turn, determines how wide the voltage pulse will be across the output transformer primary winding. This, then, controls the magnitude of the inverter output voltage.

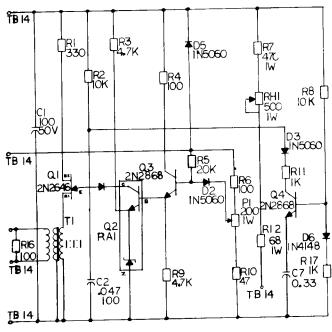

- 5) The voltage regulator circuit takes a sample of the inverter output voltage and works in conjunction with the phase control circuit to determine how much the slave flip-flop output should be delayed or advanced. This variation allows the inverter output voltage to increase or decrease slightly as required to stay constant at a pre-determined level.

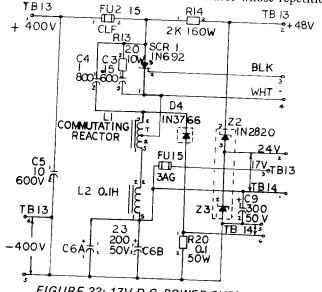

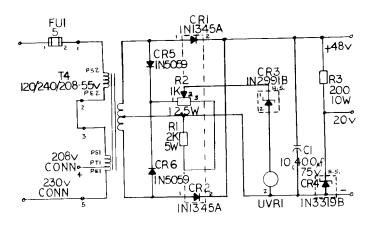

There are two electronic power supplies in the Master Control equipment. The 17 Volt "Chopper" supply energizes the master and slave flip-flop printed circuit boards, the phase control boards, pulse amplifier boards and fuse monitor. Note that a 48 Volt takeoff from the "Chopper" is used to energize the oscillator and the voltage regulator boards. The other power supply, with a 48 Volt output, feeds the printed circuit boards on the impedance inserter and the Static Switch (when used). These two power supplies are mounted on separate panels and each forms a complete subassembly. See Master Control - Section 5 for more detailed information.

\*Used on Redundant Systems Only.

#### **BATTERY**

The battery normally furnished with the UPS is the lead calcium type, consisting of 184 cells in series, per battery. This is a lead-acid battery that uses a new, improved lead calcium plate alloy. It does not require an equalizing charge and is non-gassing. The battery remains connected to the DC bus at all times to immediately assume load if the commercial power source fails. It will furnish power to maintain rated UPS output for the time required and will be recharged by the rectifier battery charger upon return of the commercial power source. The battery protection consists of a circuit breaker sized to handle the continuous current required by the inverter and also the short circuit amperes from the battery. As in common station battery practice, the cells are situated in a rack which can be two or three tiers. These racks can be arranged back-to-back or end-toend.

# **TURN-ON PROCEDURE BATTERY CHARGERS**

With commercial power available and properly connected to the UPS, begin the turn-on procedure with the Battery Charger(s) and proceed as follows:

- 1) Close the control power switches to start the cooling fans, energize logic and protective circuits and the gate pulse generator and regulator circuits.

- 2) Turn Mode Selector switch to the "Automatic" posi-

- 3) Turn current limit potentiometer R79 on the instrument door completely CCW.

- 4) Close the AC breaker.

- 5) Turn the current limit potentiometer (R79) CW until the DC Voltmeter reads 405 Volts.

- 6) Perform Steps 1 through 5 for the redundant Battery Charger (If any).

- 7) Close the Battery breaker.

- 8) Turn the current limit potentiometer R79 completely

The battery charger(s) are now paralleled with the station battery on the DC bus input to the inverter(s). Continue turn-on procedure with the Master Control and Inverter(s) as follows, starting with the inverter which supplies 208 Volts AC input to the 48 Volt DC supply in the Master Control:

- Close the single pole knife switch in the Master Control section to energize excitation circuits for the pulse generator and regulator circuits. This also provides power for the inverter indicating lamp and alarm circuits.

- 2) Close the double pole knife switch in the DC input unit of the Inverter.

- 3) Close the DC input breaker. After a short time delay, the DC contactor closes and seals in. This action is automatic. The Inverter output voltage will build up to rated value.

- 4) Check for rated AC voltage on all three phases.

- 5) Close the AC output breaker connecting the inverter to the critical bus.

- 6) Close the Impedance Inserter (ZI).

- 7) Perform Steps 2 through 6 for the redundant inverter, if any. Note: The voltage may have to be adjusted after closing onto the critical bus.

#### TURN-OFF PROCEDURE

Begin with the Inverter and Master Control and proceed as follows:

- 1) Open the AC output breaker.

- 2) Open the DC input breaker.

- 3) Wait 5 seconds and open the control power knife switch in the DC input unit of the inverter.

- 4) Repeat Steps 1 through 3 for the redundant Inverter(s), if any.

- 5) Open the knife switch in the Master Control section.

Normally the Battery Charger is left connected to the battery in order to maintain required charging current to it.

However, if this also is to be shut down for maintenance or cleaning:

- 1) Open the battery breaker.

- 2) Turn the current limit potentiometer (R79) on the door completely CCW.

- 3) Open the AC breaker.

- 4) Repeat Steps 1 through 3 for the redundant Battery Charger(s), if any.

- 5) Open the control power switches.

#### MONITORING OF VOLTAGES

This important function is performed by various voltage relays which detect abnormal conditions at critical locations throughout the equipment. The more common are listed here although additional devices may be added for any one particular equipment.

- a) On the 17 Volt Power Supply (Chopper): These instantaneous type relays (Type PJV) monitor the output of this critical supply. They are de-energized if the 17 Volt output is lost, and prevent start-up of the inverters until the condition is corrected.

- b) On the 48 Volt Power Supply: These instantaneous type relays monitor the output of this supply which feeds the impedance inserter control. They initiate transfer to the bypass switchgear (when present) if the 48 Volt output is lost.

- c) On the DC bus: Instantaneous undervoltage relays (Type NGV) shut down the system by tripping the AC and DC circuit breakers whenever this bus voltage drops below the 320 Volt level. These relays also prevent start-up of the inverter if this DC voltage is not at least at that level.

- d) On the DC bus: Instantaneous overvoltage relays (Type NGV) trip the AC input breaker on the battery charger if an overvoltage occurs at this location.

- e) On the inverter AC output: Induction disk relays (Type IAV) (if supplied) are of the overvoltage-undervoltage type. They operate to initiate a transfer to by-pass switchgear on incipient failure of inverter output voltage.

#### **MAINTENANCE**

A periodic routine of cleaning and inspection should be established. Such cleaning is necessary to prevent faulty operation of a device due to accumulation of dust or corrosion. Inspections should be more frequent if the demands on the equipment are exacting. Under normal conditions, the protective devices do not operate; therefore these devices need careful inspection. Remove dust from all modules & components with a vacuum cleaner or blow out with compressed air.

The listing below is intended as a general guide when

visually checking electrical equipment. Frequently such a check will detect a faulty component before its failure causes an outage:

| COMPONENT                | LOOK FOR                                                               |

|--------------------------|------------------------------------------------------------------------|

| Resistors                | Broken, blackened, loose connections                                   |

| Capacitors               | Bulged, leaking, loose connections                                     |

| Diodes, Transis-<br>tors | Broken, loose connections                                              |

| Printed Ckt.<br>Boards   | Black spots around components, loose connections, gaps in solder runs. |

| Pushbuttons<br>&Switches | Binds in shaft, broken or burned contacts                              |

| Relays                   | Charring around coil, dirty contacts                                   |

| Instruments              | Broken case or cover, bent needle                                      |

| Terminal Blocks          | Cracks, loose connections                                              |

| Wire & Cable             | Cracks in insulation, exposed conductor, loose terminations            |

| Contactors               | Charring around coil, dirty contacts                                   |

| Fan Motors               | Binds in bearings, loose connections                                   |

| Circuit Breakers         | Broken arc chutes, dirty contacts                                      |

| Transformers             | Charred insulation, loose connections                                  |

| Bus Joints               | Should be tight. Use contact grease if remaking joint.                 |

#### **SECTION 2: BATTERY CHARGER**

#### GENERAL INFORMATION

The battery charger is used with the UPS system to charge the electrical storage battery and to furnish DC current to the inverter. The battery charger utilizes a rectifying circuit to convert electrical energy at power frequency to a nominal 405 Volts DC to charge the storage battery. The rectifying elements of the battery charger are silicon controlled rectifiers which are arranged in a three phase full wave bridge circuit. The battery charger equipment is a specifically modified version of the General Electric Silcomatic regulated rectifier.

REFERENCES: GEK-17540 - General Instruction, Inspection and Test Procedures for Silcomatic I.

GEK-13595 - General Instruction, Inspection and Test Procedures for Silcomatic II.

#### DESCRIPTION OF COMPONENTS

Each battery charger contains the following components:

1) A rectifier transformer used for isolation purposes and to step down the incoming line voltage to the level needed for proper operation.

- 2) SCR rectifier circuit to convert the incoming AC power to DC power.

- 3) A DC filter section to smooth out the DC voltage to the load.

- 4) A DC potential transformer module (DCPT) to obtain a voltage feedback signal.

- 5) A DC current transformer (DCCT) to obtain a current feedback signal.

- 6) Regulator-Amplifier Tray Board used to amplify error signal and to produce a DC control signal to control the gate pulse generator.

- 7) Gate pulse generator tray board to generate pulses for the gating of the thyristors.

- 8) DC Circuit Breaker, AK-2-50X, manual operation.

- 9) Instrumentation

- a) DC Voltmeter 0-500 VDC scale.

- b) DC Ammeter suitable scale.

- 10) Controls

- a) Green light to indicate breaker open.

Red light to indicate breaker closed.

- b) Alarm Switch: An alarm circuit is provided from the battery charger input breaker to the master control section of the UPS. This alarm is activated whenever the input AC breaker in the battery charger is tripped. The alarm switch, disables this circuit. The AC breaker will be tripped under any of the following conditions:

- 1) DC overvoltage

- 2) Fan failure

- 3) Transformer overtemperature

- 4) Loss of 46 V DC supply

- c) Indicating Lights

- 1) YIL-1 "Control Volts OK"

- 2) WIL-1 "Loss of Cooling Air"

- 3) WIL-2 "Transformer Overtemperature"

- 4) CIL-3 "Capacitor Fuse"

- 5) WIL-3 "DC Overvoltage"

- d) Current limit adjustment, on the door of each charger.

- e) "Manual Auto" switch, places battery charger in one of the two modes of operation.

- f) "Manual Voltage Adjust" Rheostat Adjust battery charger's output volts when charger is in manual operation.

- g) RHF rheostat on the DCPT tray Adjust unit output volts when battery charger is in automatic operation.

- h) Reset switch for DC overvoltage circuit.

#### **OPERATION**

The incoming power from the Utility Company or from the auxiliary power (Diesel Generators) is fed to the AC bus. The battery charger is connected to AC incoming bus through the input circuit breaker, which is a manually operated device. With the closing of this circuit breaker, the transformer T1 decreases the voltage from 480 VAC to 356 VAC. Transformer T1 is delta-wye connected and feeds into the SCR (Silicon Controlled Rectifiers) modules for rectification.

An SCR is a phase controlled rectifying device which is controlled by applying a signal to the gate lead during the positive half cycle. This causes the SCR to conduct as an ordinary rectifier. When the applied AC voltage reverses in the polarity (anode to cathode of the SCR), the SCR will turn off until the next gate signal is applied.

A filter circuit is placed in the output to limit ripple voltage. The power supply is protected against normal voltage transients, such as produced by switching and other line disturbances, by surge suppressors connected to both the AC and DC buses. A manual operated DC circuit breaker (AK-2-50X) is used for the output disconnect.

Refer to GEK-17540 or GEK-13595 for completely detailed information on Silcomatic operation.

#### **TURN-ON PROCEDURE**

The start-up procedure given below is for starting the battery chargers only. For the procedure to start the entire UPS, see Section I.

- 1. Check Transfer Switch.\*

- 2. Turn Alarm Switch to "ON" Position.

- 3. Turn Current Limit Potentiometer (On the instrument door) all the way CCW.

- 4. Close AC Breaker in the switchgear (Breaker can only be closed manually).

- 5. Turn Current Limit Potentiometer CW until the DC voltmeter reads 405 VDC.

- 6. Close the DC Breaker (AK-2-50X) in the battery charger.

- 7. Close the Battery Breaker in the switchgear. Note: Do not reverse the order of 6 & 7.

- 8. Turn Current Limit Potentiometer all the way CW.

- \* If Transfer Switch is in the "Auto" position, the battery charger will be voltage regulated at a voltage determined by the setting of the RHF rheostat in the front of the DCPT tray, and with a current limit determined by the setting of R79 on the door of the battery charger. If the Transfer Switch is in "Manual" position, the battery charger will operate at an output voltage determined by the "Manual Voltage Adjust" rheostat. CAUTION must be exercised, though, as there is no indication of unit voltage until it is higher than battery voltage and as the regulator is by-passed, there is no current limit on the unit. The battery chargers must be operated in the "Auto" position when connected to the inverters.

#### **OVERVOLTAGE ADJUSTMENT**

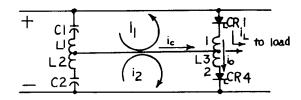

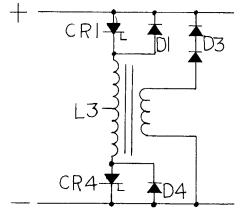

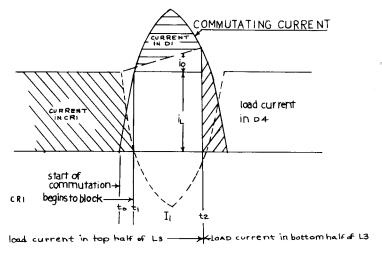

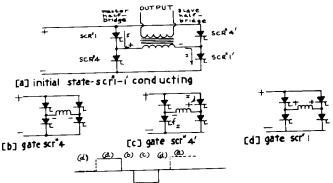

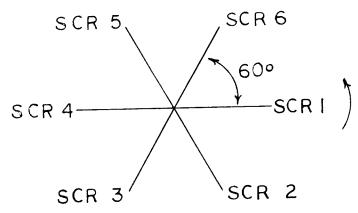

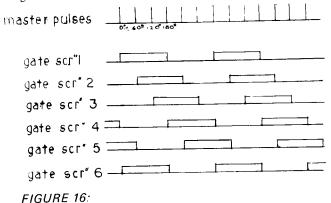

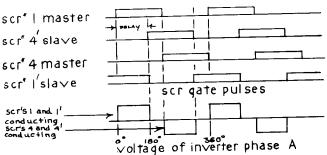

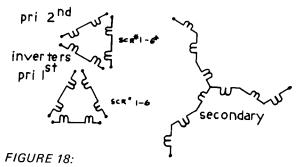

The overvoltage alarm was factory set for 420 Volts DC.